High-Level Synthesis

Lead: Antonino Tumeo

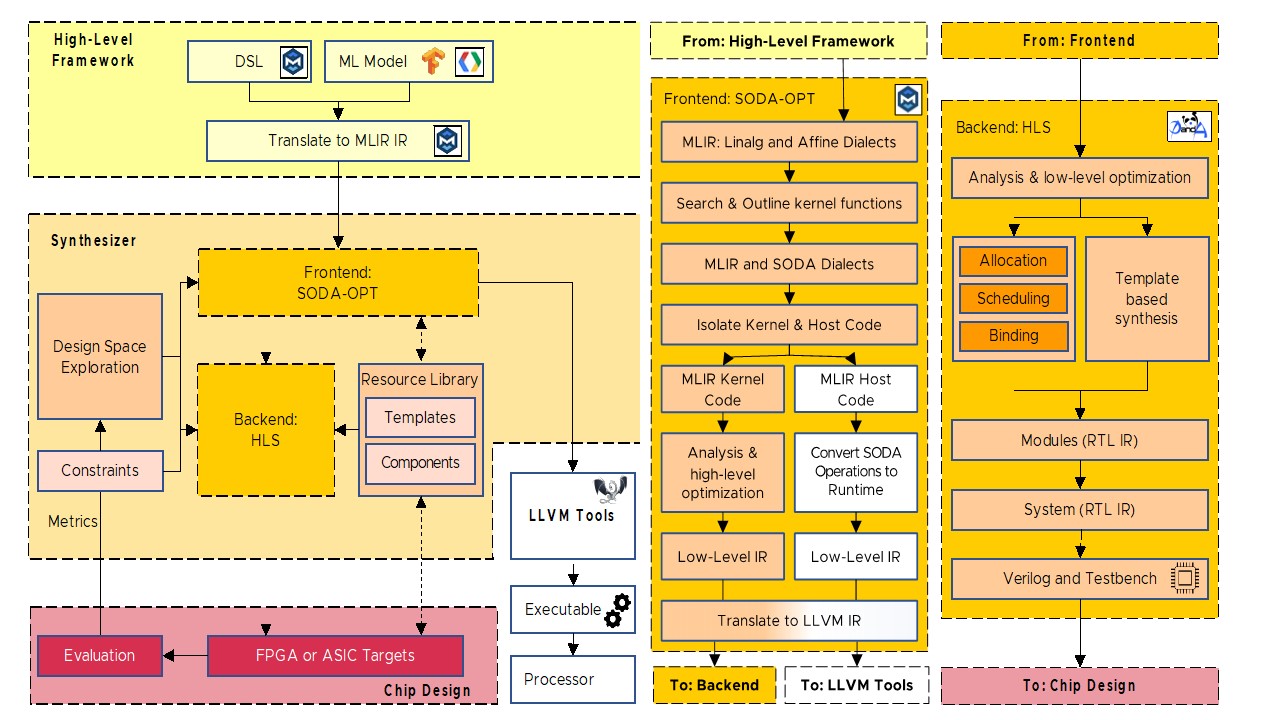

High-level synthesis (HLS) enables the generation of hardware designs starting from algorithmic descriptions in high-level languages and programming frameworks. Our researchers developed a suite of software tools—the Software Defined Architectures (SODA) Synthesizer—that empowers domain scientists to design their own specialized architectures and accelerators. The SODA Synthesizer is an open-source, modular, multilevel, end-to-end compiler from high-level frameworks to silicon that provides an environment for researchers to experiment with new ideas in system-level design and HLS. The SODA Synthesizer is composed of a set of interoperating tools, including SODA-Opt, a compiler based frontend, PandA-Bambu, a state-of-the art HLS research tool PandA-Bambu, and OpenCGRA, a unified flow for modeling, testing, and evaluating Coarse Grained Reconfigurable Arrays (CGRA) designs. The entire toolchain can generate Verilog optimized for Field Programmable Gate Arrays (FPGAs) from all the major vendors (AMD/Xilinx, Intel/Altera, NanoExplore, Lattice) or interface with commercial and open-source logic synthesis tools for Application-Specific Integrated Circuits (ASICs), including OpenROAD flow with the FreePDK 45 nm library and the ASAP 7 nm predictive library.

SODA-Opt is a tool that enables identifying segments of applications written in high-level productive programming frameworks (Python, Machine Learning) for hardware acceleration through high-level synthesis tools or hardware generators like OpenCGRA.

OpenCGRA is an open-source unified framework for modeling, testing, and evaluating specialized Coarse-Grained Reconfigurable Arrays (CGRAs). OpenCGRA also supports a design space exploration flow for specializing CGRA designs, architectures to scale out CGRA systems, and mechanisms to support partial dynamic reconfiguration for data streaming applications.

PandA-Bambu includes two significant contributions lead by PNNL:

Svelto is a high-level synthesis methodology for the automated generation of high-throughput accelerators for graph analytics and irregular computation.

HLS of Task Parallel Specification is a High-Level Synthesis methodology that generates specialized accelerators starting from high-level parallel programs. The methodology combines statically scheduled accelerators in a dataflow architecture.

Publications:

- SODA Synthesizer:

- Zhang J., N. Bohm Agostini, S. Song, C. Tan, A.M. Limaye, V.C. Amatya, and J.B. Manzano Franco, et al. 2021. "Towards Automatic and Agile AI/ML Accelerator Design with End-to-End Synthesis." IEEE 32nd International Conference on Application-specific Systems, Architectures and Processors (ASAP 2021), July 7-9, 2021, Virtual, 218-225. Piscataway, New Jersey:IEEE. PNNL-SA-163507. doi:10.1109/ASAP52443.2021.00040

- Nicolas Bohm Agostini, Serena Curzel, Jeff Zhang, Ankur Limaye, Cheng Tan, Vinay Amatya, Marco Minutoli, Vito Giovanni Castellana, Joseph Manzano, David Brooks, Gu-Yeon Wei, Antonino Tumeo,"Bridging Python to Silicon: The SODA Toolchain" in IEEE Micro, vol. , no. 01, pp. 1-1, 5555. doi: 10.1109/MM.2022.3178580 (preprint)

- Serena Curzel, Nicolas Bohm Agostini, Antonino Tumeo, Fabrizio Ferrandi: Hardware acceleration of complex machine learning models through modern high-level synthesis. CF 2022: 209-210

- Bambu

- Ferrandi F., V.G. Castellana, S. Curzel, P. Fezzardi, M. Fiorito, M. Lattuada, and M. Minutoli, et al. 2021. "Invited: Bambu: an Open-Source Research Framework for the High-Level Synthesis of Complex Applications." 58th ACM/IEEE Design Automation Conference (DAC 2021), December 5-9, 2021, San Francisco, CA, 1327-1330. Piscataway, New Jersey:IEEE. PNNL-SA-160619. doi:10.1109/DAC18074.2021.9586110

- SODA-Opt

- Nicolas Bohm Agostini, Serena Curzel, David R. Kaeli, Antonino Tumeo: SODA-OPT an MLIR based flow for co-design and high-level synthesis. CF 2022: 201-202 (Best Poster Award)

- OpenCGRA

- Tan C., C. Xie, A. Li, K.J. Barker, and A. Tumeo. 2020. "OpenCGRA: An Open-Source Unified Framework for Modeling,Testing, and Evaluating CGRAs." IEEE 38th International Conference on Computer Design (ICCD 2020), October 18-21, 2020, 381-388. Piscataway, New Jersey:IEEE. PNNL-SA-152863. doi:10.1109/ICCD50377.2020.00070

- Cheng Tan, Chenhao Xie, Ang Li, Kevin J. Barker, Antonino Tumeo: AURORA: Automated Refinement of Coarse-Grained Reconfigurable Accelerators. DATE 2021: 1388-1393

- Cheng Tan, Tong Geng, Chenhao Xie, Nicolas Bohm Agostini, Jiajia Li, Ang Li, Kevin J. Barker, Antonino Tumeo: DynPaC: Coarse-Grained, Dynamic, and Partially Reconfigurable Array for Streaming Applications. ICCD 2021: 33-40 (Best Paper Award)

- Cheng Tan, Nicolas Bohm Agostini, Jeff Zhang, Marco Minutoli, Vito Giovanni Castellana, Chenhao Xie, Tong Geng, Ang Li, Kevin J. Barker, Antonino Tumeo: OpenCGRA: Democratizing Coarse-Grained Reconfigurable Arrays. ASAP 2021: 149-155

- Cheng Tan, Chenhao Xie, Tong Geng, Andres Marquez, Antonino Tumeo, Kevin J. Barker, Ang Li: ARENA: Asynchronous Reconfigurable Accelerator Ring to Enable Data-Centric Parallel Computing. IEEE Trans. Parallel Distributed Syst. 32(12): 2880-2892 (2021)

- Cheng Tan, Nicolas Bohm Agostini, Tong Geng, Chenhao Xie, Jiajia Li, Ang Li, Kevin J. Barker, Antonino Tumeo: DRIPS: Dynamic Rebalancing of Pipelined Streaming Applications on CGRAs. HPCA 2022: 304-316. 2021

- Svelto

- Minutoli, M., Castellana, V. G., Saporetti, N., Devecchi, S., Lattuada, M., Fezzardi, P., Tumeo, A., & Ferrandi, F. (2022). Svelto: High-Level Synthesis of Multi-Threaded Accelerators for Graph Analytics. In IEEE Transactions on Computers (Vol. 71, Issue 3, pp. 520–533). Institute of Electrical and Electronics Engineers (IEEE). doi:10.1109/tc.2021.3057860

- HLS of Task Parallel Specification

- Castellana V.G., A. Tumeo, and F. Ferrandi. 2021."High-Level Synthesis of Parallel Specifications Coupling Static and Dynamic Controllers." IEEE International Parallel & Distributed Processing Symposium (IPDPS 2021), May 17-21, 2021, Virtual, Online, Paper No. 9460500. Piscataway, New Jersey:IEEE.PNNL-SA-157406. doi:10.1109/IPDPS49936.2021.00028