PNNL Computer Scientists Have Paper Accepted to MICRO-53

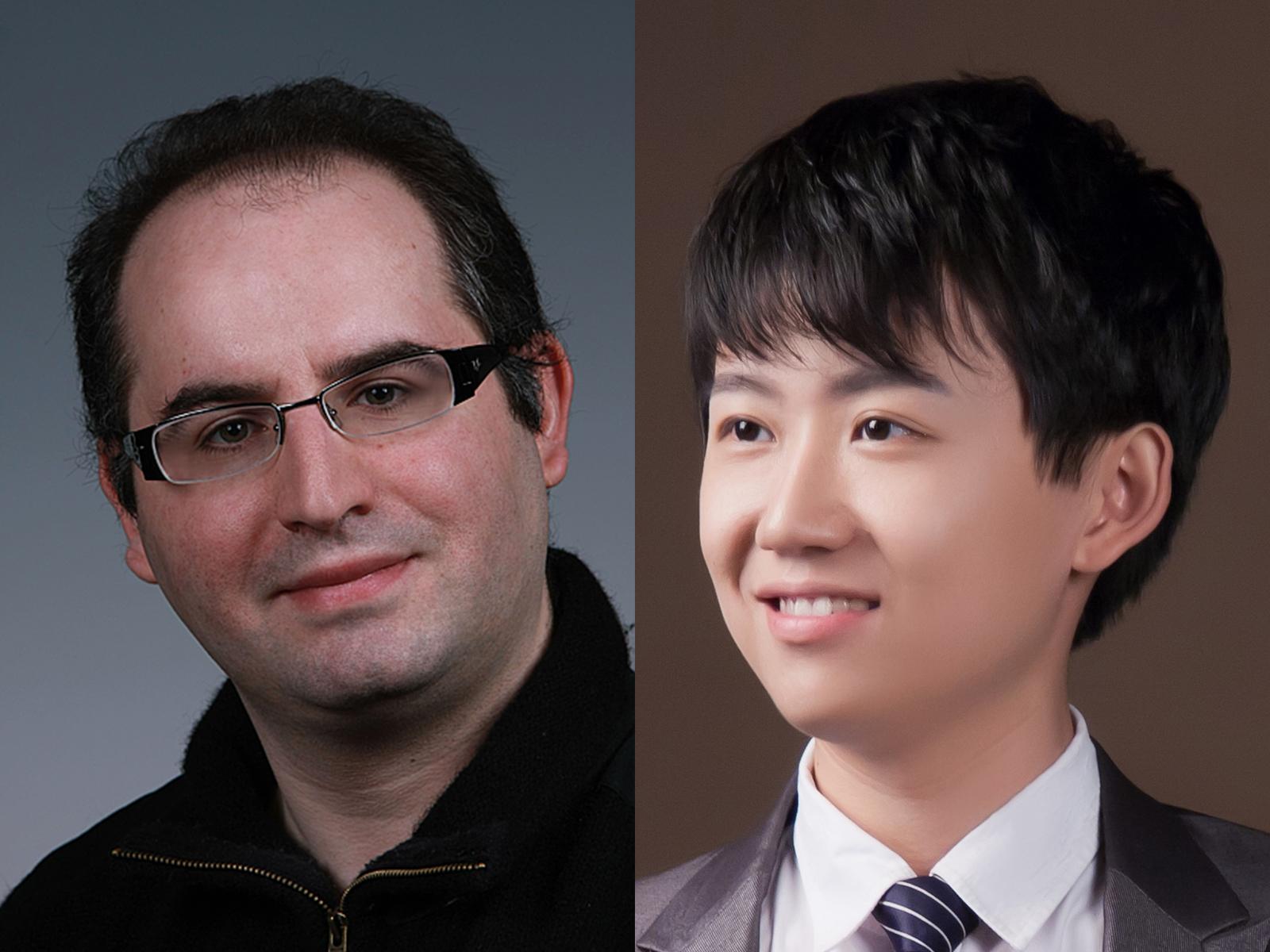

Ang Li and Antonino Tumeo will present hardware to balance machine learning workloads at a top computer architecture conference

PNNL computer scientists, Ang Li and Antonino Tumeo, published at the 53rd Institute of Electrical and Electronics Engineers/Association for Computing Machinery International Symposium on Microarchitecture, a top conference for computer architecture also known as MICRO-53.

The paper is part of their work on the development of accelerators for machine learning models on sparse data structures. This paper, led by Tong Geng who was previously an intern at PNNL and advised by Li, is the first work to present hardware—rather than software—techniques to automatically rebalance workloads at runtime for machine learning on graphs.

Graphs are a convenient way to represent large amounts of interconnected data from fields ranging from communication and transportation to biological and power grid networks. Existing high-performance computers already struggle to perform large-scale data discovery on real-world graphs due to fine-grained, unpredictable data accesses and highly unbalanced data distribution. Graph convolutional networks are an emerging neural network architecture able to learn from graphs. To improve the efficiency of these networks on high-performance computers, the researchers designed an accelerator that automatically rebalances the workload among the parallel processing units. The accelerator infers patterns in the graph data at runtime through a custom hardware component, thus achieving considerable speedups in learning with graph convolutional networks.

The paper, titled “AWB-GCN: A Graph Convolutional Network Accelerator with Runtime Workload Rebalancing,” was co-authored with colleagues at Microsoft, Boston University, Zhejiang University, and the University of Hong Kong.

Published: July 27, 2020