PNNL-38817

# Electromagnetic Transient Modeling of Large Data Centers for Grid-Level Studies

Alpha Release

January 2026

Brett A. Ross

Jim Follum

U.S. DEPARTMENT

of ENERGY

Prepared for the U.S. Department of Energy

under Contract DE-AC05-76RL01830

## DISCLAIMER

This report was prepared as an account of work sponsored by an agency of the United States Government. Neither the United States Government nor any agency thereof, nor Battelle Memorial Institute, nor any of their employees, makes **any warranty, express or implied, or assumes any legal liability or responsibility for the accuracy, completeness, or usefulness of any information, apparatus, product, or process disclosed, or represents that its use would not infringe privately owned rights.** Reference herein to any specific commercial product, process, or service by trade name, trademark, manufacturer, or otherwise does not necessarily constitute or imply its endorsement, recommendation, or favoring by the United States Government or any agency thereof, or Battelle Memorial Institute. The views and opinions of authors expressed herein do not necessarily state or reflect those of the United States Government or any agency thereof.

PACIFIC NORTHWEST NATIONAL LABORATORY

*operated by*

BATTELLE

*for the*

UNITED STATES DEPARTMENT OF ENERGY

*under Contract DE-AC05-76RL01830*

Printed in the United States of America

Available to DOE and DOE contractors from

the Office of Scientific and Technical Information,

P.O. Box 62, Oak Ridge, TN 37831-0062

[www.osti.gov](http://www.osti.gov)

ph: (865) 576-8401

fox: (865) 576-5728

email: [reports@osti.gov](mailto:reports@osti.gov)

Available to the public from the National Technical Information Service

5301 Shawnee Rd., Alexandria, VA 22312

ph: (800) 553-NTIS (6847)

or (703) 605-6000

email: [info@ntis.gov](mailto:info@ntis.gov)

Online ordering: <http://www.ntis.gov>

# **Electromagnetic Transient Modeling of Large Data Centers for Grid-Level Studies**

Alpha Release

December 2025

Brett A. Ross

Jim Follum

Prepared for

the U.S. Department of Energy

under Contract DE-AC05-76RL01830

Pacific Northwest National Laboratory

Richland, Washington 99354

## Abstract

The magnitude and complexity of electricity usage patterns from large data centers are having significant impacts on the operation and dynamics of the power grid; grid operators and planners require a range of specialized data center models to properly evaluate these impacts and specify technical solutions as needed. Towards addressing this need, Pacific Northwest National Laboratory (PNNL) has developed a library of electromagnetic transient (EMT) models for grid-level studies of data centers called the data center model library (DML). This report describes how the DML was created and how it may properly be used.

The models present in the DML are generic models; subject matter expertise and additional technical data are needed to modify these models before they can represent any real data center. However, they will significantly reduce the level of effort required to develop site-specific models and can serve as a common starting point to guide industry towards a more refined consensus.

Most of the models within DML are dedicated to representing the power electronics interfaces commonly used in modern data centers, such as double-conversion uninterruptible power supplies and single-phase power factor correction converters. These models are intended for use in grid-level studies and are a simplified aggregation of many small components. That said, background material on the physical and electrical design of large data centers is provided as companion material so that users can be aware of many of the details which have been omitted or streamlined as a matter of practical necessity. Additionally, guidance on the application of EMT analysis for data center interconnection studies is provided, which aids users in identifying when the DML is necessary and what sort of additional model development may be necessary for conducting real-world studies.

## Acknowledgments

This work was funded by the Department of Energy's Office of Electricity as a part of Foundational Studies and Technical Solutions for Large Digital Dynamic Loads. We would like to extend special thanks to Sandra Jenkins and Nathaniel Horner for their support and guidance.

Development of these models would not have been possible without the expertise of a great many experts from numerous industries. The authors would like to extend special thanks to individuals who shared experiences and insights that were particularly valuable. This report does not necessarily reflect the views of the acknowledged people or their affiliates.

|                                              |                                                                   |                                                        |                                               |

|----------------------------------------------|-------------------------------------------------------------------|--------------------------------------------------------|-----------------------------------------------|

| <b>Amazon Web Services</b>                   | Siva Prakash                                                      | <b>Mitsubishi Electric</b>                             | Kay Chen                                      |

| <b>Dominion Energy</b>                       | Katelynn Vance<br>Rahul Chakraborty                               | <b>New England Independent System Operator</b>         | Kannan Sreenivasachar                         |

|                                              |                                                                   | <b>North American Electric Reliability Corporation</b> | Hasala Dharmawardena                          |

| <b>Eaton</b>                                 | Keith Watson                                                      | <b>Real-Time Digital Simulators</b>                    | Sumek Elimban                                 |

| <b>Electranix</b>                            | Andrew Isaacs                                                     | <b>Schneider Electric</b>                              | Andre Felipe Silva Melo                       |

| <b>Electric Power Research Institute</b>     | Parag Mitra<br>Lakshmi Sundaresh                                  | <b>Southern Company</b>                                | Sudip Manandhar<br>Harish Sharma              |

| <b>Electric Reliability Council of Texas</b> | Prashant Kansal<br>Jonathan Rose<br>Eric Meier<br>Patrick Gravois | <b>Tesla</b>                                           | Sai Gopal Vennelaganti                        |

|                                              |                                                                   | <b>Texas A&amp;M University</b>                        | Prasad N. Enjeti<br>Xiaoyang Wang<br>Xin Chen |

| <b>Idaho Power</b>                           | Paul Ortmann                                                      | <b>University of Idaho</b>                             | Brian K. Johnson                              |

| <b>Microsoft</b>                             | Scot Heath                                                        | <b>Vertiv</b>                                          | Greg Ratcliffe                                |

Additionally, we would like to gratefully acknowledge the value of venues such as the NERC LLTF, NERC LMWG, ERCOT LMWG, IEEE PSRC, and Open Rack Compute projects. These forums have enabled open dialog and information sharing which have also been essential to the development of these models.

## Acronyms and Abbreviations

|       |                                                 |

|-------|-------------------------------------------------|

| AI    | Artificial intelligence                         |

| AVM   | Average-value model                             |

| ASIC  | Application-specific integrated circuit         |

| BoP   | Balance of plant                                |

| CPU   | Central processing unit                         |

| CRAH  | Compute-rack air handler                        |

| DC    | Direct current                                  |

| DML   | Data center modeling library                    |

| EMT   | Electromagnetic transient                       |

| ESIG  | Energy Systems Integration Group                |

| ESS   | Energy storage system                           |

| FACTS | Flexible AC transmission systems                |

| GFL   | Grid following                                  |

| GFM   | Grid forming                                    |

| GPU   | Graphics processing unit                        |

| GSU   | Generator step-up                               |

| HV    | High voltage                                    |

| IBR   | Inverter-based resource                         |

| IT    | Information technology                          |

| ITE   | Information technology equipment                |

| LLTF  | Large loads task force                          |

| LV    | Low voltage                                     |

| LVDC  | Low voltage direct current                      |

| LVRT  | Low voltage ride through                        |

| NERC  | North American Electric Reliability Corporation |

| NPC   | Neutral-point clamped                           |

| MMC   | Multi-level modular converter                   |

| MV    | Medium voltage                                  |

| OEM   | Original equipment manufacturer                 |

| PCC   | Point of common coupling                        |

| PFC   | Power factor correction                         |

| PH    | Phase                                           |

| PLL   | Phase-locked loop                               |

| PWM   | Pulse-width modulation                          |

| SSCI  | Subsynchronous control interaction              |

| SSTI  | Subsynchronous torsional interaction            |

| SST   | Solid-state transformer                         |

| SWM   | Switching model                                 |

| UPS   | Uninterruptible power supply                    |

| VSC   | Voltage-source converter                        |

## Contents

|                                                              |     |

|--------------------------------------------------------------|-----|

| Abstract.....                                                | iii |

| Acknowledgments.....                                         | iv  |

| Acronyms and Abbreviations.....                              | v   |

| 1.0 Introduction .....                                       | 1   |

| 2.0 Data center Power Systems .....                          | 2   |

| 2.1 Power Electronics Topologies.....                        | 2   |

| 2.2 Balance of Plant.....                                    | 8   |

| 3.0 Electromagnetic Transient Modeling of Data centers.....  | 13  |

| 3.1 EMT studies for Data center Interconnection .....        | 13  |

| 3.1.1 Oscillatory Interactions .....                         | 13  |

| 3.1.2 Regulation of Voltage and Frequency.....               | 18  |

| 3.1.3 Power Quality .....                                    | 19  |

| 3.2 Suitability of DML Specifically .....                    | 21  |

| 4.0 Model Overview.....                                      | 22  |

| 4.1 IT Loads.....                                            | 25  |

| 4.1.1 Uninterruptible Power Supplies.....                    | 26  |

| 4.1.2 ITE Power Supplies .....                               | 28  |

| 4.1.3 Short-Time Load Profiles .....                         | 32  |

| 4.1.4 Implications of DC Distribution.....                   | 37  |

| 4.2 Climate Control Loads .....                              | 37  |

| 4.3 Site Support Load .....                                  | 39  |

| 4.3.1 Balance of Plant .....                                 | 39  |

| 4.3.2 Energy Storage Systems .....                           | 39  |

| 5.0 Power System Models.....                                 | 43  |

| 5.1 Inverter Model Demonstration (DML_Inverter_Demo).....    | 43  |

| 5.2 DC-DC Converter Demonstration (DML_DC_DC_Demo) .....     | 45  |

| 5.3 PFC Converter Demonstration (DML_PFC_Demo).....          | 46  |

| 5.4 Complete Data center Models.....                         | 48  |

| 5.4.1 Simple Data Center (DML_DC1_Simple).....               | 49  |

| 5.4.2 Centralized UPS Data Center (DML_DC2_Central_UPS)..... | 51  |

| 5.4.3 Distributed UPS Data Center (DML_DC3_Dist_UPS).....    | 52  |

| 6.0 Component Models .....                                   | 54  |

| 6.1 DC-DC Buck-Boost Converter (AVM) – DC_bi_avm.....        | 54  |

| 6.2 DC-DC Buck-Boost Converter (SWM) – DC_bi_swm.....        | 55  |

| 6.3 GFM Droop Control – gfm_droop.....                       | 56  |

| 6.4 GFM Droop Control w/ Vdc Reg. – gfm_droop_vdc .....      | 56  |

|      |                                                                                      |    |

|------|--------------------------------------------------------------------------------------|----|

| 6.5  | dq-Domain current regulator – <code>ireg</code> .....                                | 57 |

| 6.6  | dq-Domain Current Limiter – <code>ilim_dq</code> .....                               | 58 |

| 6.7  | 3 PH Inverter, AVM – <code>inv_avm</code> .....                                      | 59 |

| 6.8  | 3 PH Inverter, GFL – <code>inv_gfl</code> .....                                      | 60 |

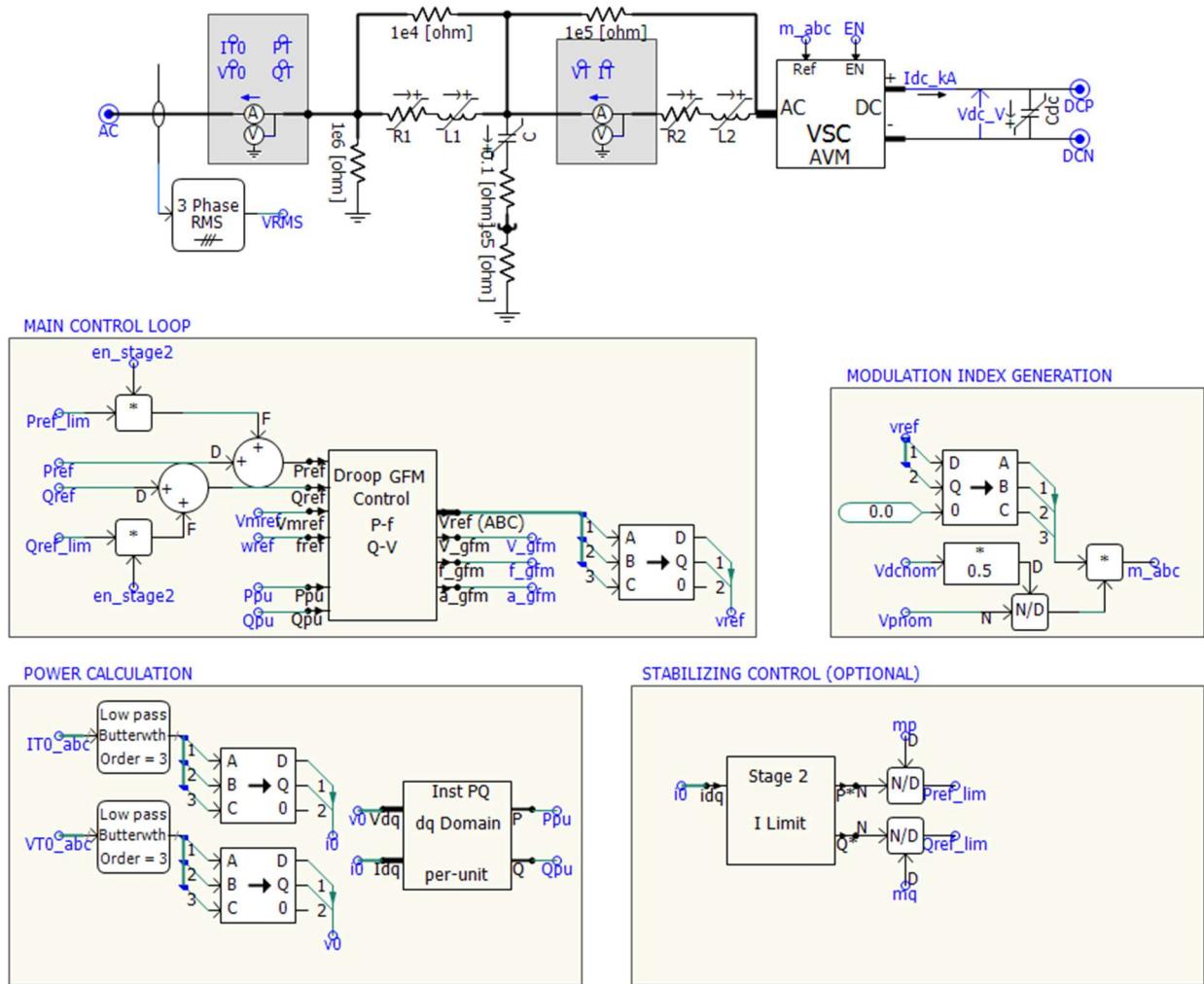

| 6.9  | 3 PH Inverter, GFM, Droop Control, AVM – <code>inv_gfm_droop_avm</code> .....        | 62 |

| 6.10 | 3 PH Inverter, GFM, Droop Control, SWM – <code>inv_gfm_droop_swm</code> .....        | 64 |

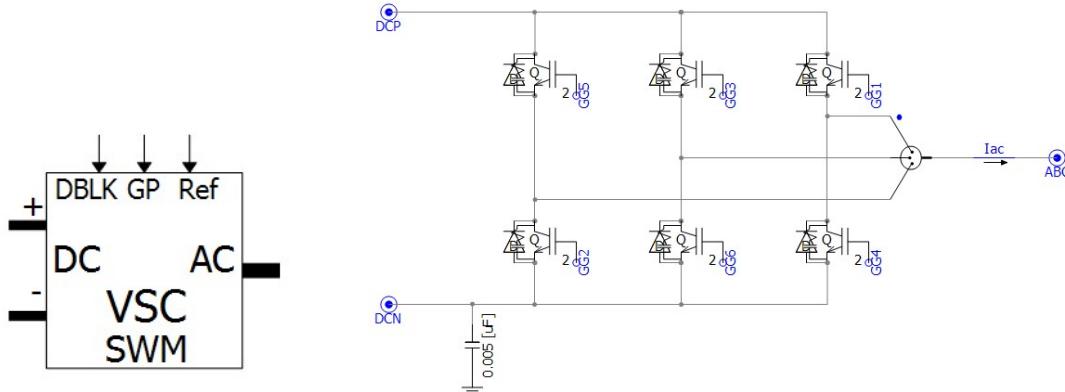

| 6.11 | 3 PH Inverter, SWM – <code>inv_swm</code> .....                                      | 65 |

| 6.12 | Variable AI Training Load – <code>load_ai_train</code> .....                         | 65 |

| 6.13 | Playback-Based Electronic Load – <code>load_playback</code> .....                    | 66 |

| 6.14 | Lumped LV Cable, 1 PH – <code>LV_cable_1PH</code> .....                              | 69 |

| 6.15 | Lumped LV Cable, 3 PH – <code>LV_cable_3PH</code> .....                              | 69 |

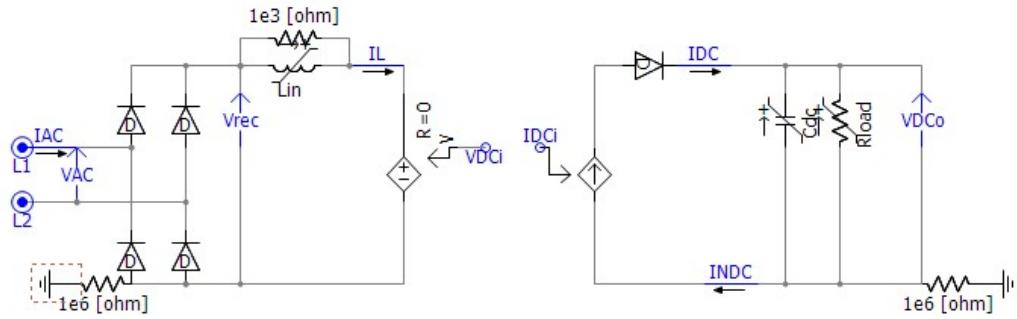

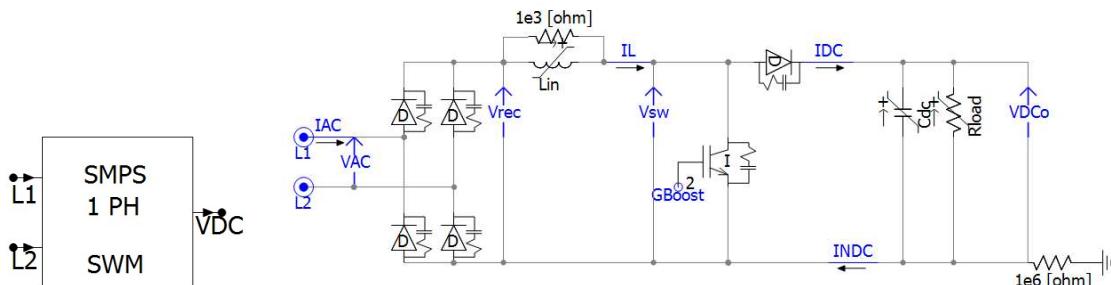

| 6.16 | 1 PH Rectifier with PFC, AVM – <code>pfc_avm</code> .....                            | 70 |

| 6.17 | 1 PH Rectifier with PFC, SWM – <code>pfc_swm</code> .....                            | 72 |

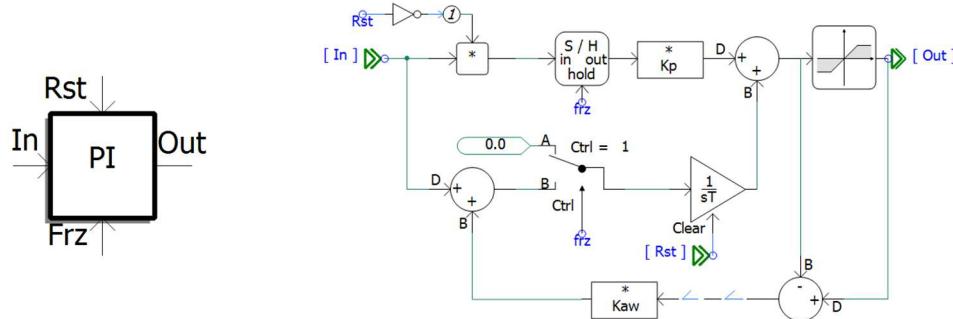

| 6.18 | PI Controller with Anti-Windup Logic – <code>PI_AntiWindUp</code> .....              | 73 |

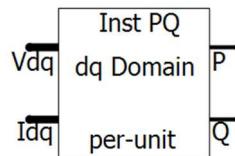

| 6.19 | dq-Domain Power Calculation – <code>PQ_dq</code> .....                               | 74 |

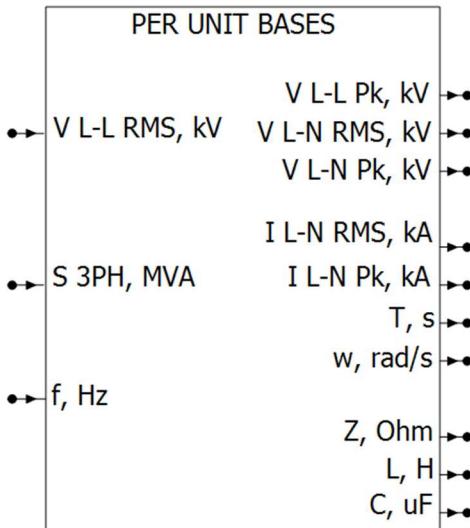

| 6.20 | Per-unit Base Calculator – <code>pu_bases</code> .....                               | 74 |

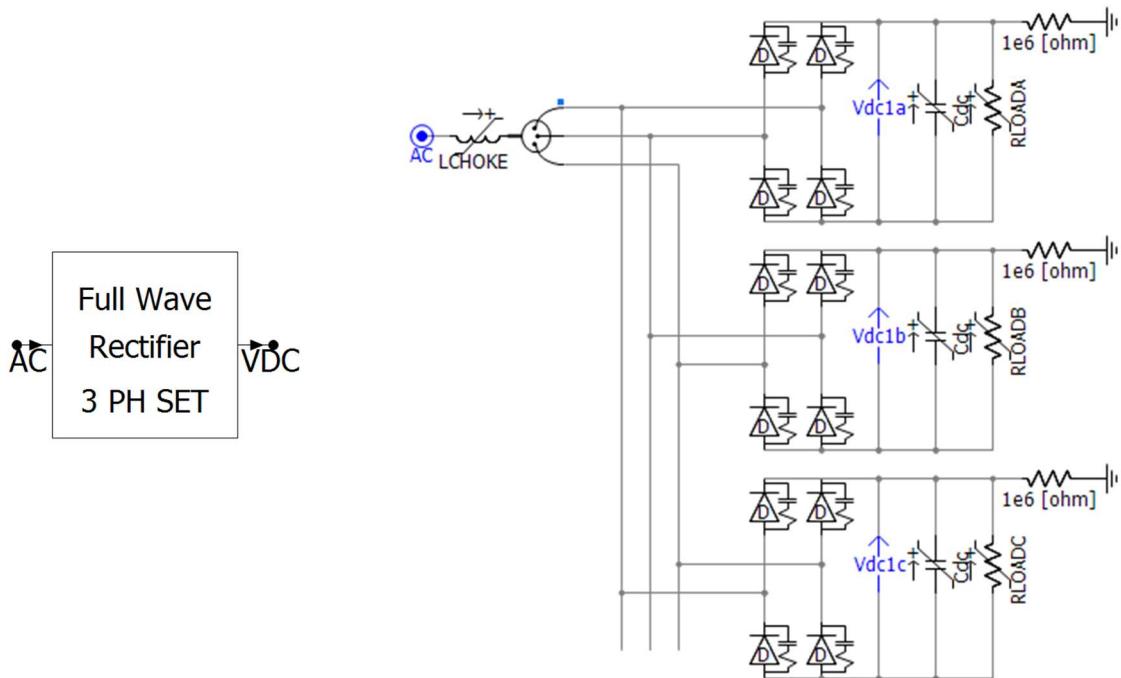

| 6.21 | 3 PH Set of 1 PH Rectifiers – <code>rect_3x_full_wave</code> .....                   | 75 |

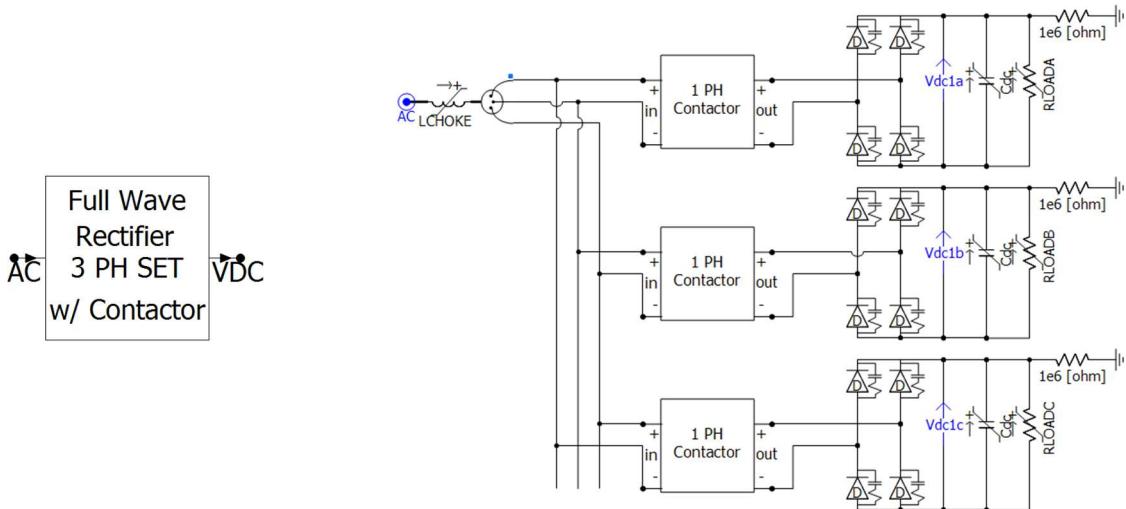

| 6.22 | 3 PH Set of 1 PH Rectifiers with Protection – <code>rect_3x_full_wave_c</code> ..... | 77 |

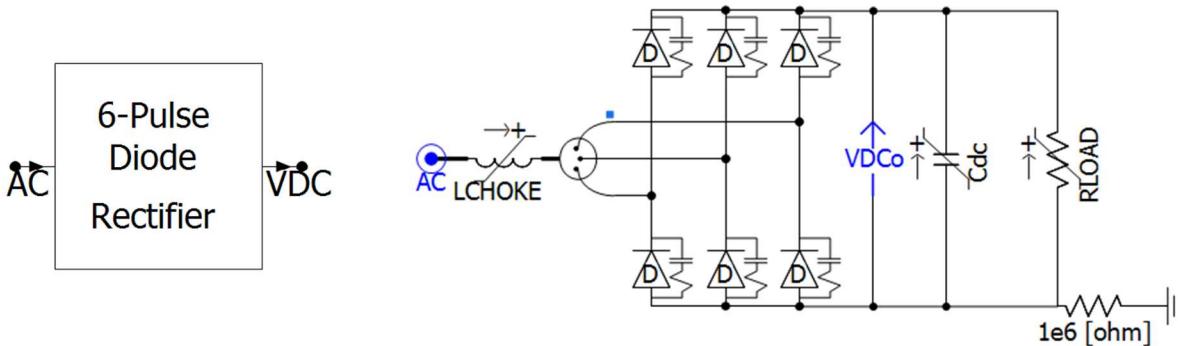

| 6.23 | 3 PH Diode Rectifier – <code>rect_six_pulse</code> .....                             | 77 |

| 6.24 | Stabilizer for Droop-Based GFM Control – <code>stage2_ilim</code> .....              | 78 |

| 6.25 | Unbalance Calculation – <code>unb_rms</code> .....                                   | 78 |

| 6.26 | UPS Controller – <code>ups_ctrl</code> .....                                         | 78 |

| 6.27 | 3 PH Contactor – <code>uv_sw</code> .....                                            | 81 |

| 6.28 | 1 PH Contactor – <code>uv_sw_1PH</code> .....                                        | 82 |

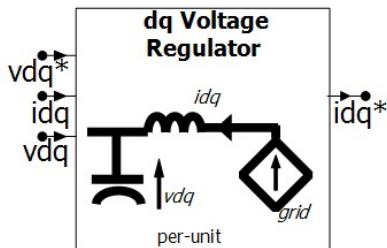

| 6.29 | dq-Domain Voltage Regulator – <code>v_reg</code> .....                               | 83 |

| 7.0  | References.....                                                                      | 84 |

## Figures

|                                                                                      |   |

|--------------------------------------------------------------------------------------|---|

| Figure 1: Single Line Diagram of Simple Data center Design .....                     | 2 |

| Figure 2: Single Line Diagram for Centralized UPS Data center Design.....            | 3 |

| Figure 3: Single Line Diagram of Distributed UPS Data center Design.....             | 4 |

| Figure 4: Single Line Diagram of Low-Voltage DC Distribution Design.....             | 5 |

| Figure 5: Single Line Diagram of Medium-Voltage Solid-State Transformer Design ..... | 6 |

| Figure 6: Single Line Diagram of Medium Voltage DC Distribution Design.....          | 7 |

| Figure 7: Exemplar substation layouts for data center HV substations .....           | 8 |

| Figure 8: Single Line Diagrams for medium-voltage compute and cooling blocks .....   | 9 |

|                                                                                                                                                                                                         |    |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 9: Simplified layout of LV electrical distribution within data hall. ....                                                                                                                        | 10 |

| Figure 10: Electrical room housing 28 MW of UPS capacity [20]. ....                                                                                                                                     | 10 |

| Figure 11: Electrical room for medium-sized data center [21]. ....                                                                                                                                      | 10 |

| Figure 12: Representative data hall [22]. This facility is rated for tens of megawatts, Tier IV reliability, and LEED Gold efficiency. ....                                                             | 11 |

| Figure 13: Representative data hall [23]. This facility uses a high power density design and features hot-aisle containment. ....                                                                       | 11 |

| Figure 14: Mechanical room housing compute room air handlers (CRAH) [20]. ....                                                                                                                          | 12 |

| Figure 15: Large rooftop chiller unit for [20]. ....                                                                                                                                                    | 12 |

| Figure 16: Essential elements of an oscillatory interaction—excitation, damping, and at least two energy storage elements. ....                                                                         | 14 |

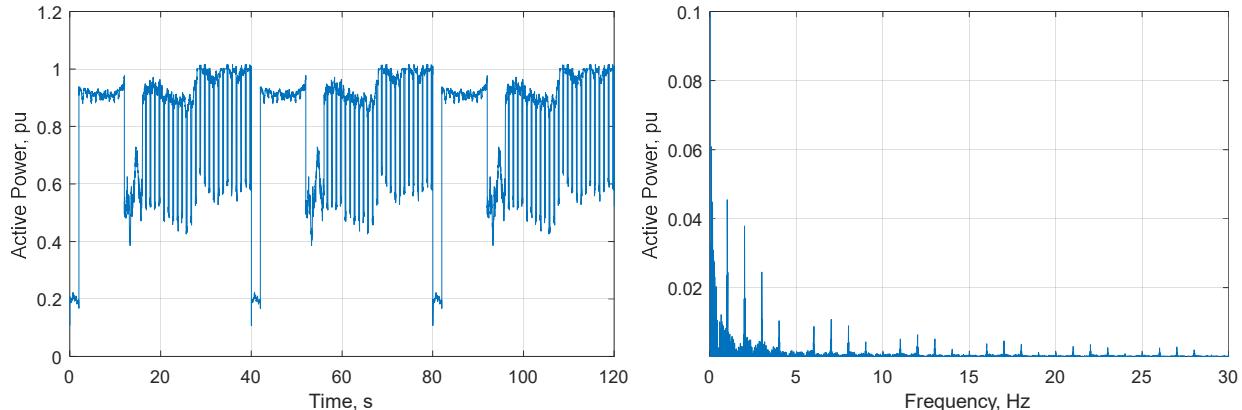

| Figure 17: Exemplar Active Power Waveform for AI Training (left) and its frequency spectrum (right). ....                                                                                               | 17 |

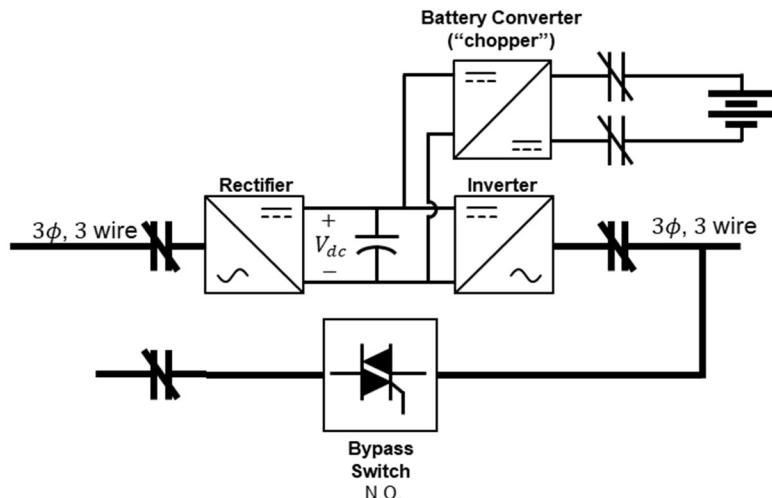

| Figure 18: Major components of double-conversion UPS. ....                                                                                                                                              | 26 |

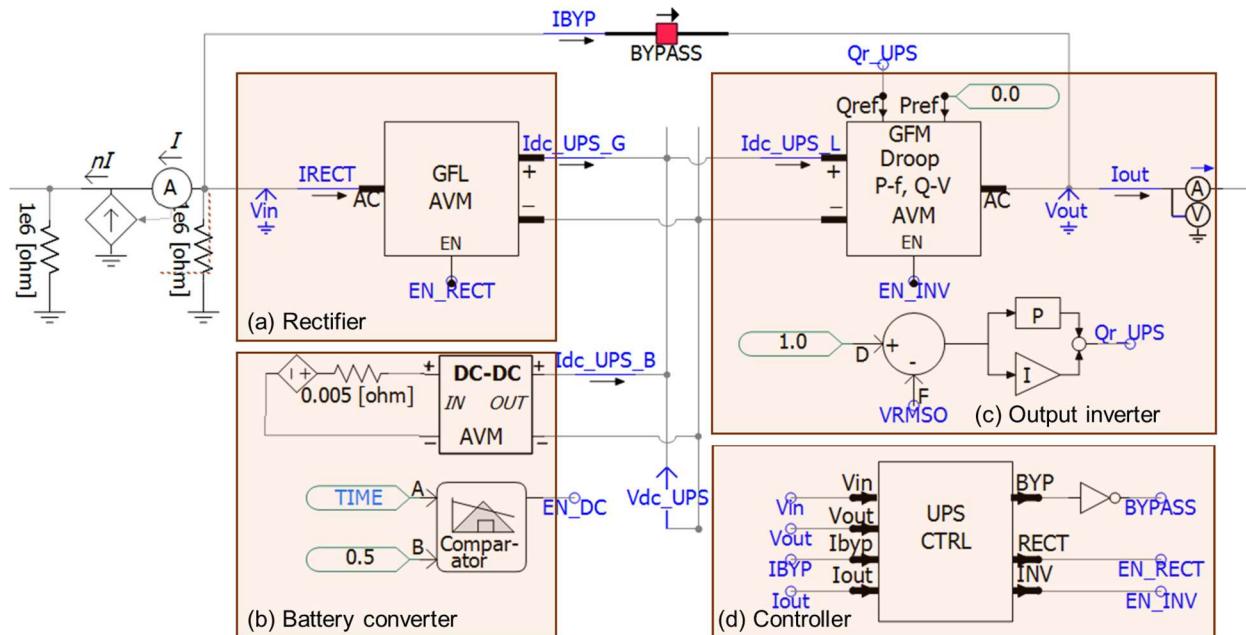

| Figure 19: Use of DML components to represent 3-phase double-conversion UPS. ....                                                                                                                       | 27 |

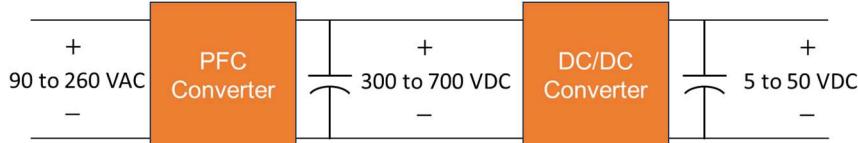

| Figure 20: Simplified power supply diagram with notional voltage levels. ....                                                                                                                           | 29 |

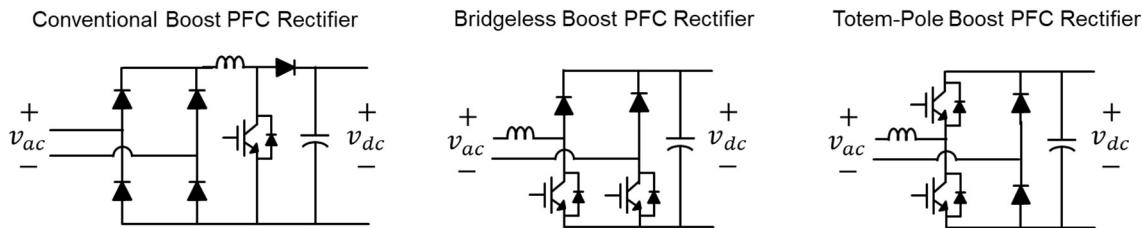

| Figure 21: Common variations of Unidirectional PFC converters. ....                                                                                                                                     | 29 |

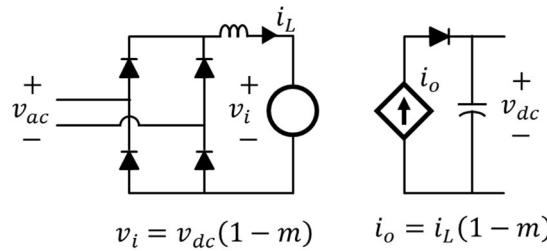

| Figure 22: AVM for unidirectional boost PFC rectifiers. ....                                                                                                                                            | 29 |

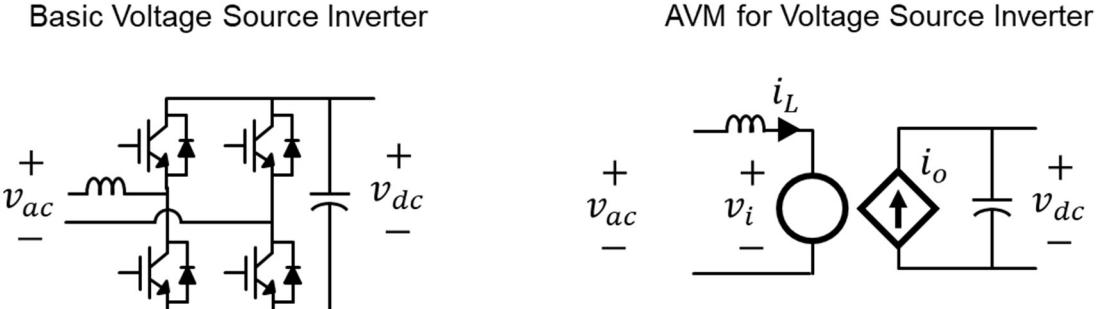

| Figure 23: Basic voltage source inverter topology (left) and its AVM (right). ....                                                                                                                      | 30 |

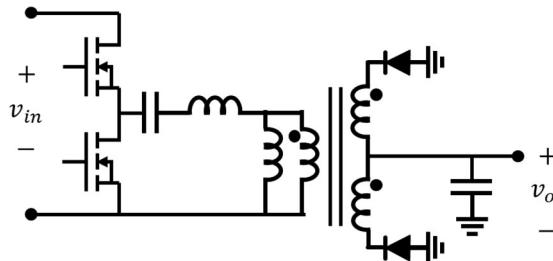

| Figure 24: Schematic of basic LLC converter. ....                                                                                                                                                       | 30 |

| Figure 25: Schematic of High Frequency Transformer for DC-DC conversion. ....                                                                                                                           | 31 |

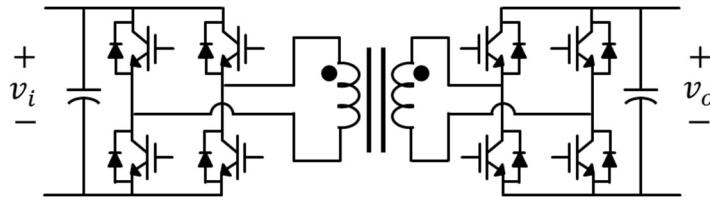

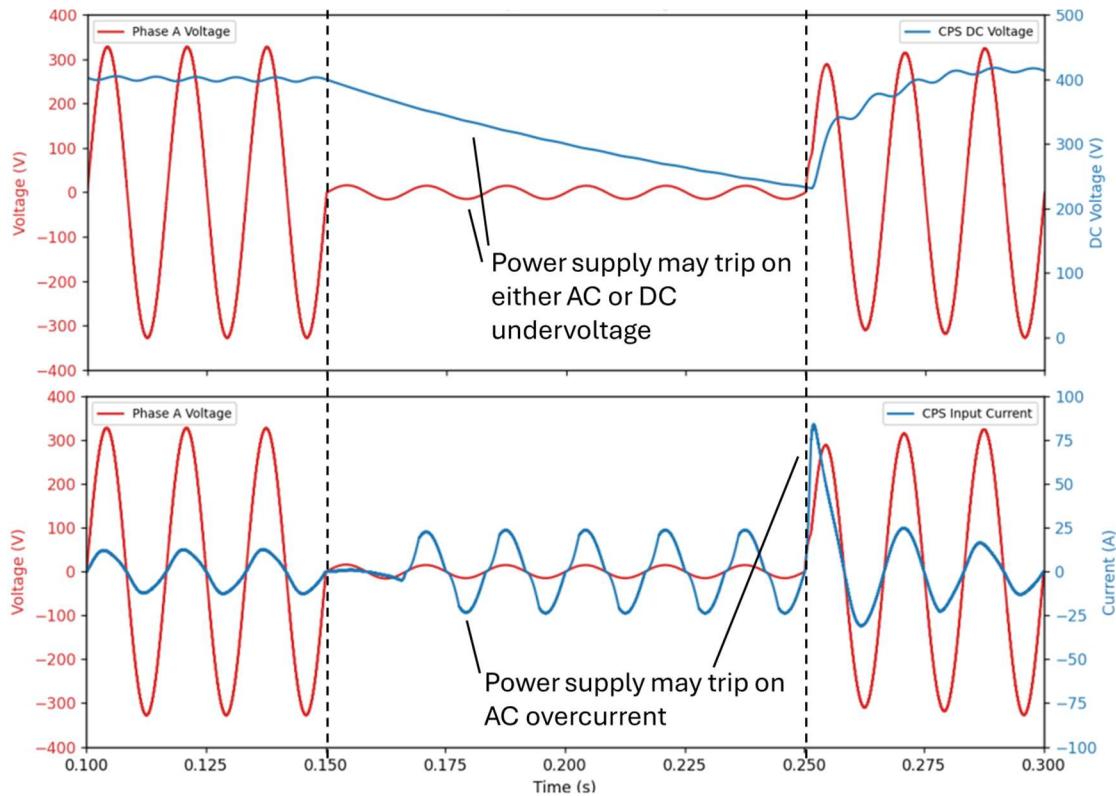

| Figure 26: Example response of PFC converter (called the “CPS” in the figure legend) to severe AC voltage sag [49]. Annotations indicate features which may cause protection functions to operate. .... | 33 |

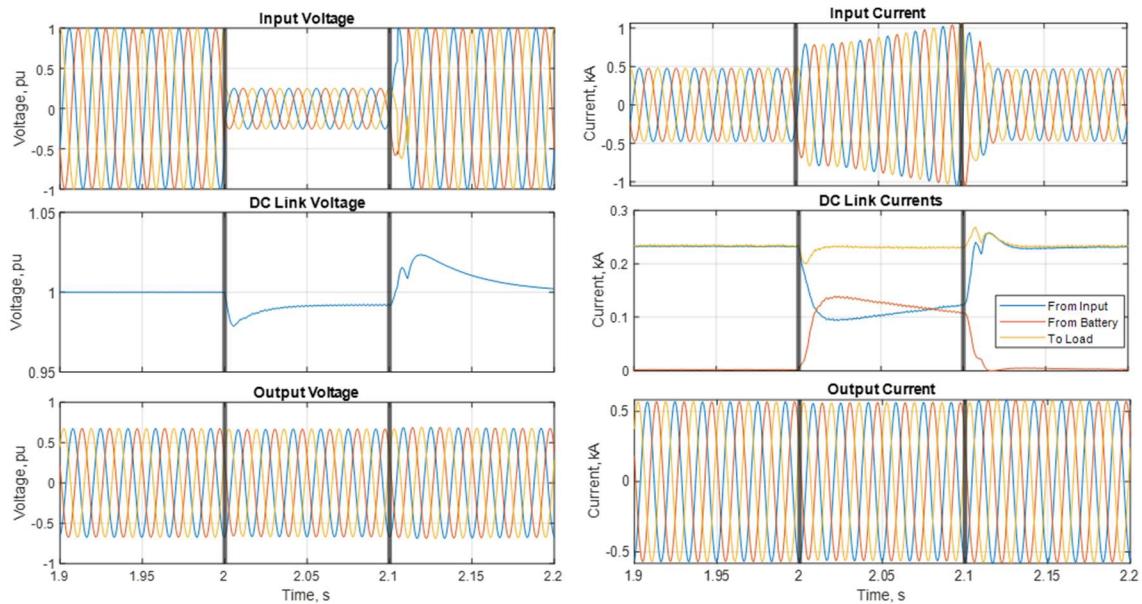

| Figure 27: Simulated response of double-conversion UPS configured to ride-through a severe three-phase fault [49]. ....                                                                                 | 34 |

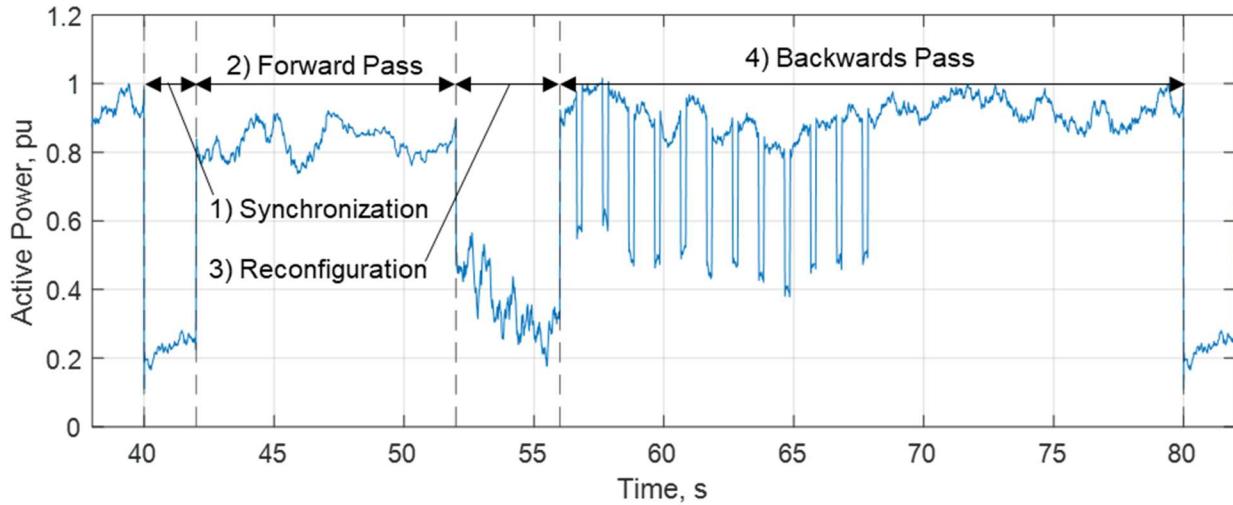

| Figure 28: Exemplar site-level active power consumption from AI training load, annotations demarcate distinct stages in the training process. ....                                                      | 36 |

| Figure 29: Five ESS deployment points for modern and near-future data centers. ....                                                                                                                     | 40 |

| Figure 30: Overview of DML_Inverter_Demo Model. ....                                                                                                                                                    | 44 |

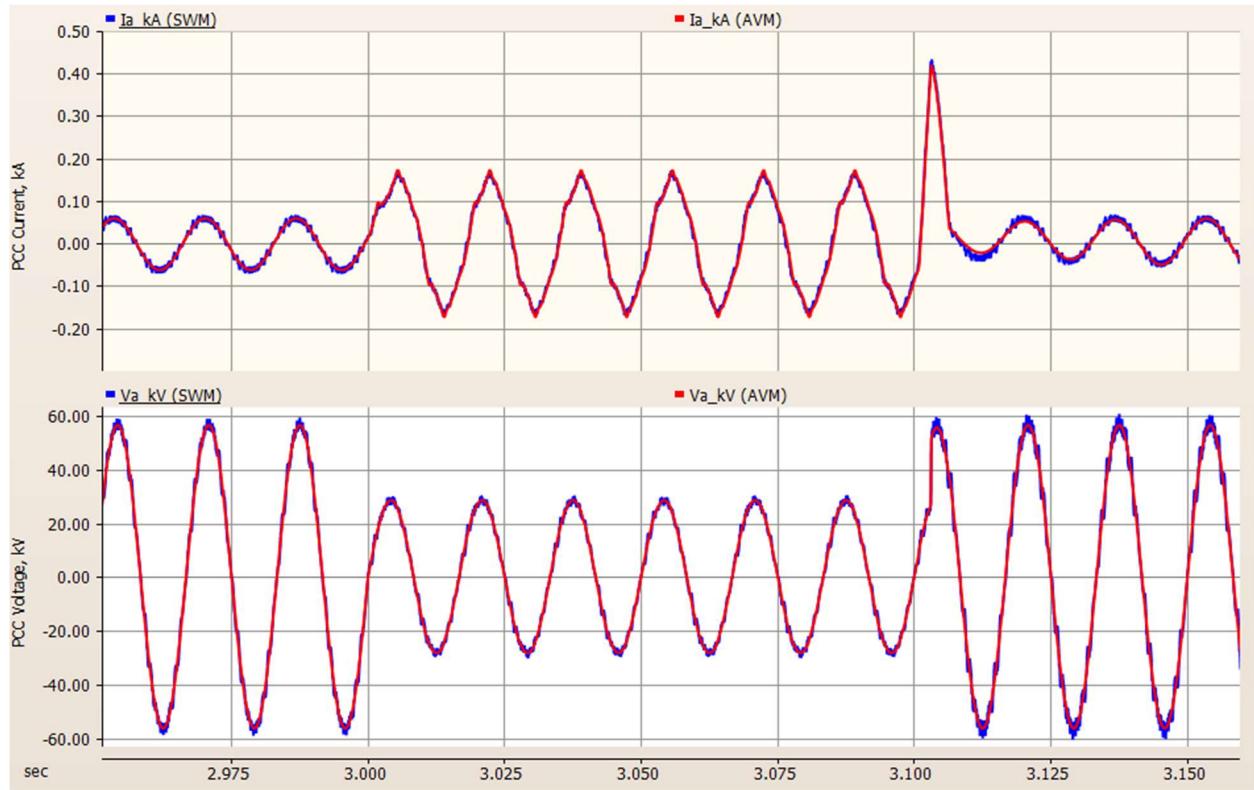

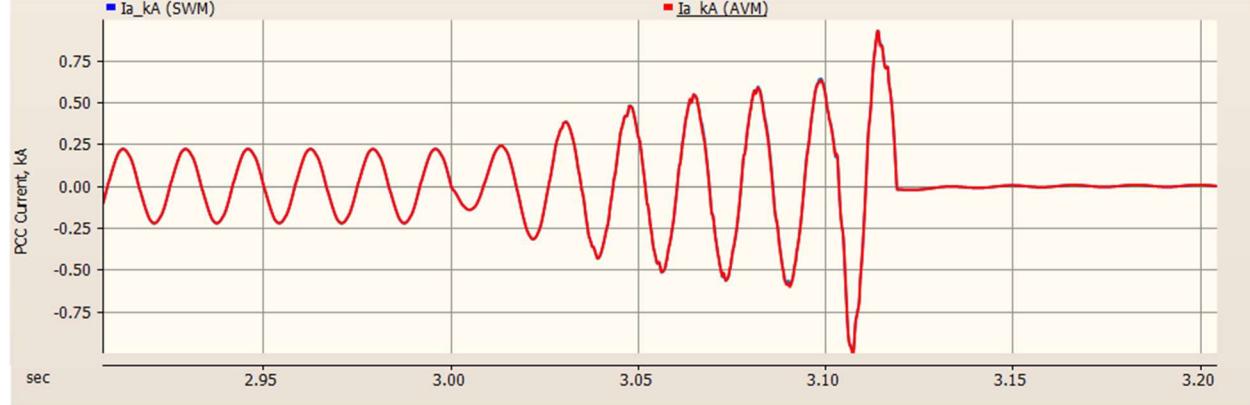

| Figure 31: Comparison of L-L fault response from <code>inv_gfm_droop_avm</code> and <code>inv_gfm_droop_swm</code> . ....                                                                               | 45 |

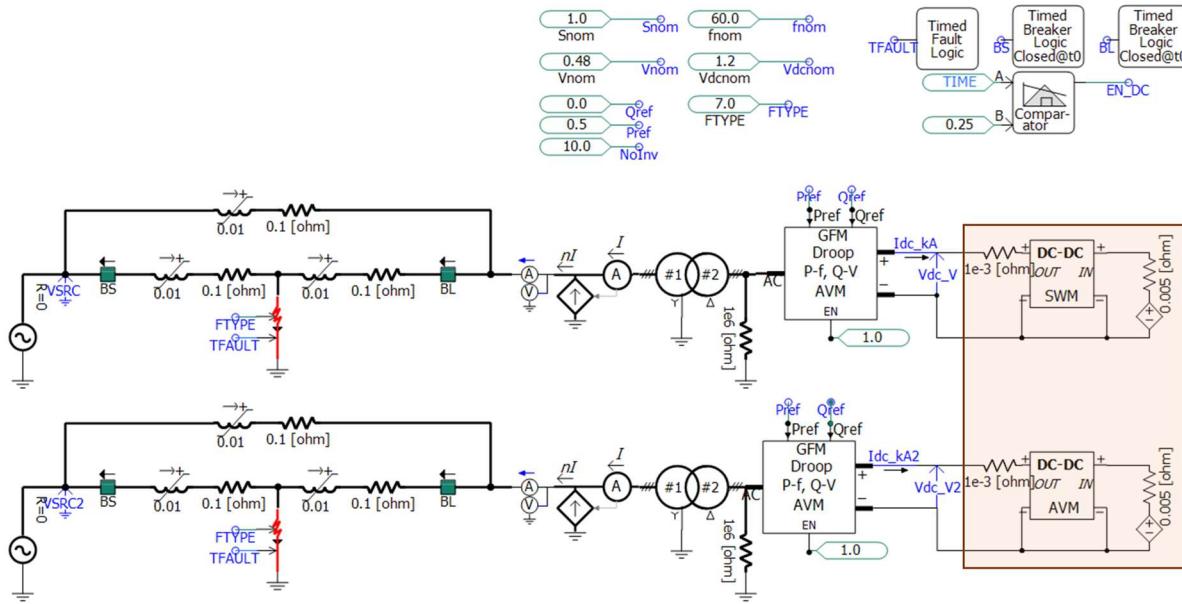

| Figure 32: Overview of DML_DC_DC_Demo Model. ....                                                                                                                                                       | 46 |

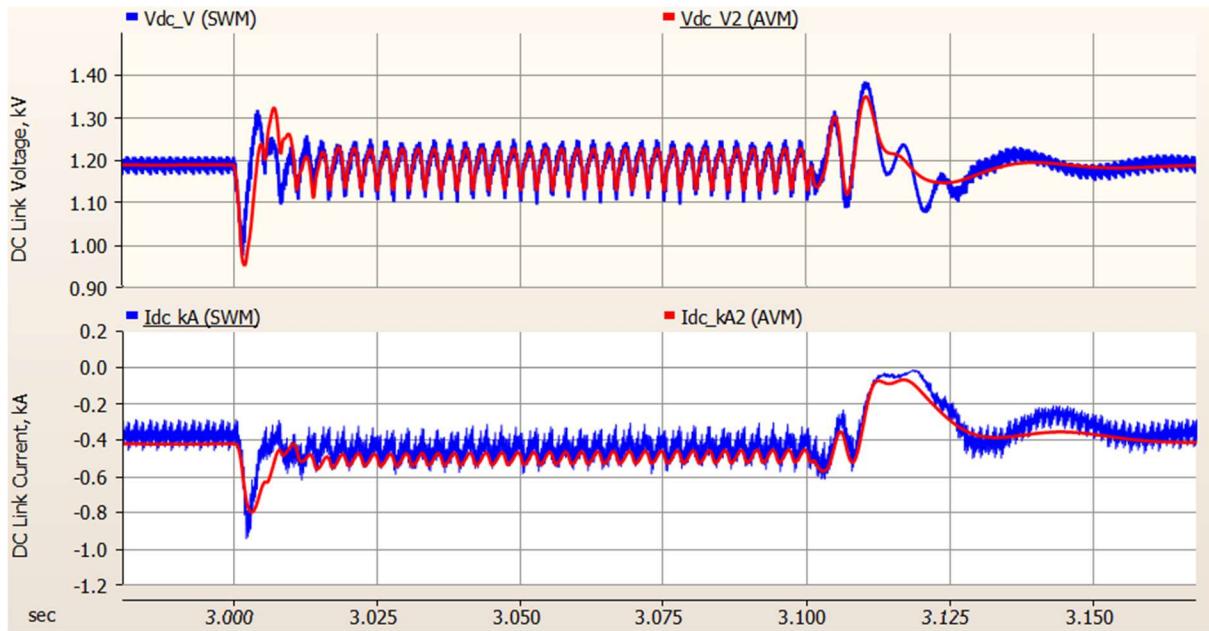

| Figure 33: Comparison of SWM (blue) and AVM (red) response to transmission system L-L fault. ....                                                                                                       | 46 |

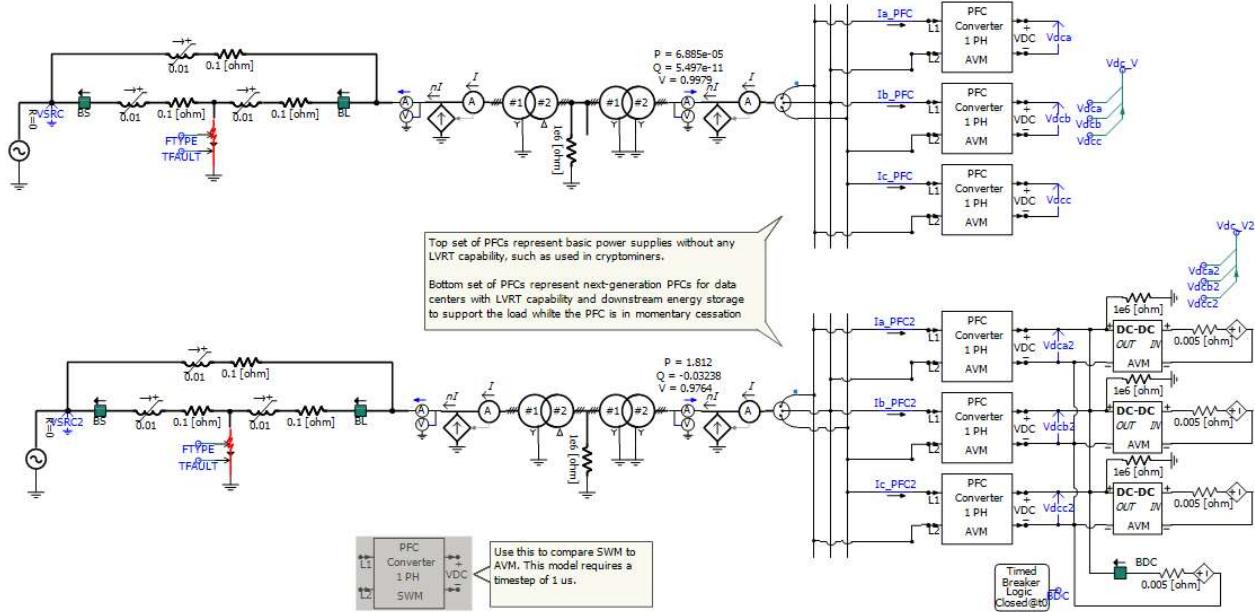

| Figure 34: Overview of the DML_PFC_Demo model. ....                                                                                                                                                     | 47 |

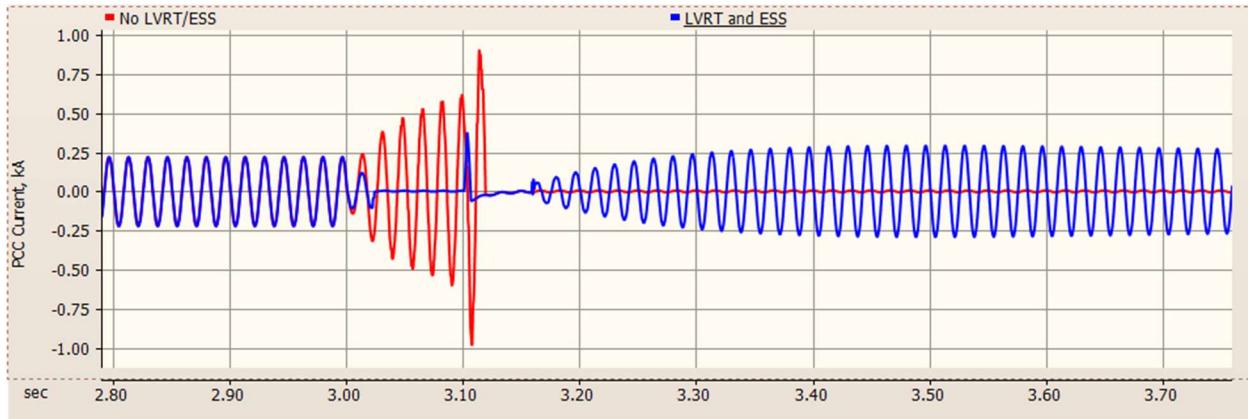

| Figure 35: Comparison of fault response of <code>pfc_avm</code> (red) and <code>pfc_swm</code> (blue) fault response. ....                                                                              | 47 |

| Figure 36: Comparison of fault response of PFC without ESS to provide LVRT (red) and with (blue). ....                                                                                                  | 48 |

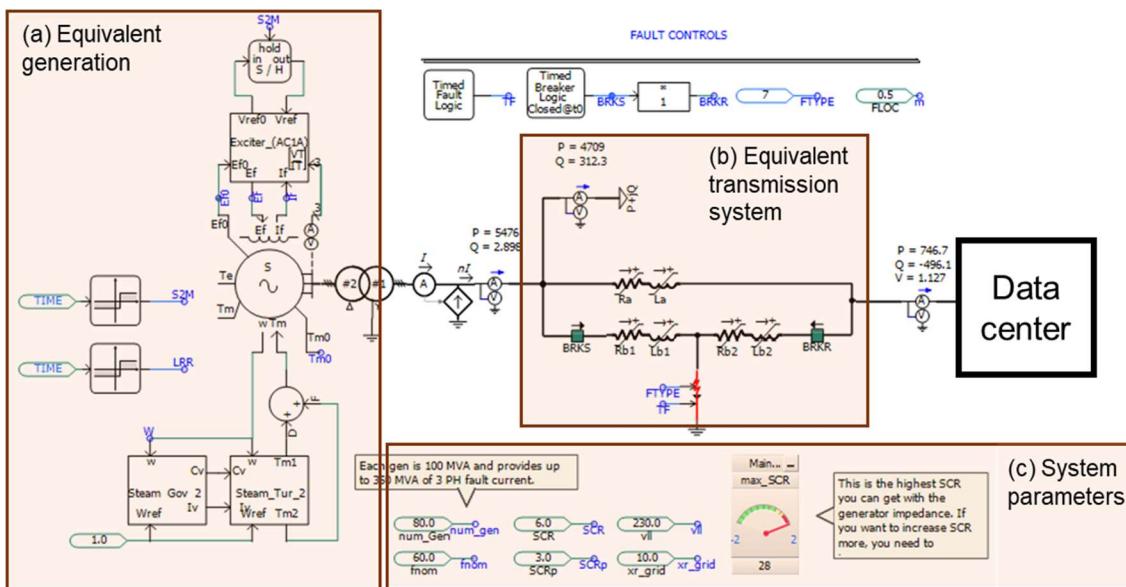

| Figure 37: Transmission system model used for complete data center models. ....                                                                                                                         | 48 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |    |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

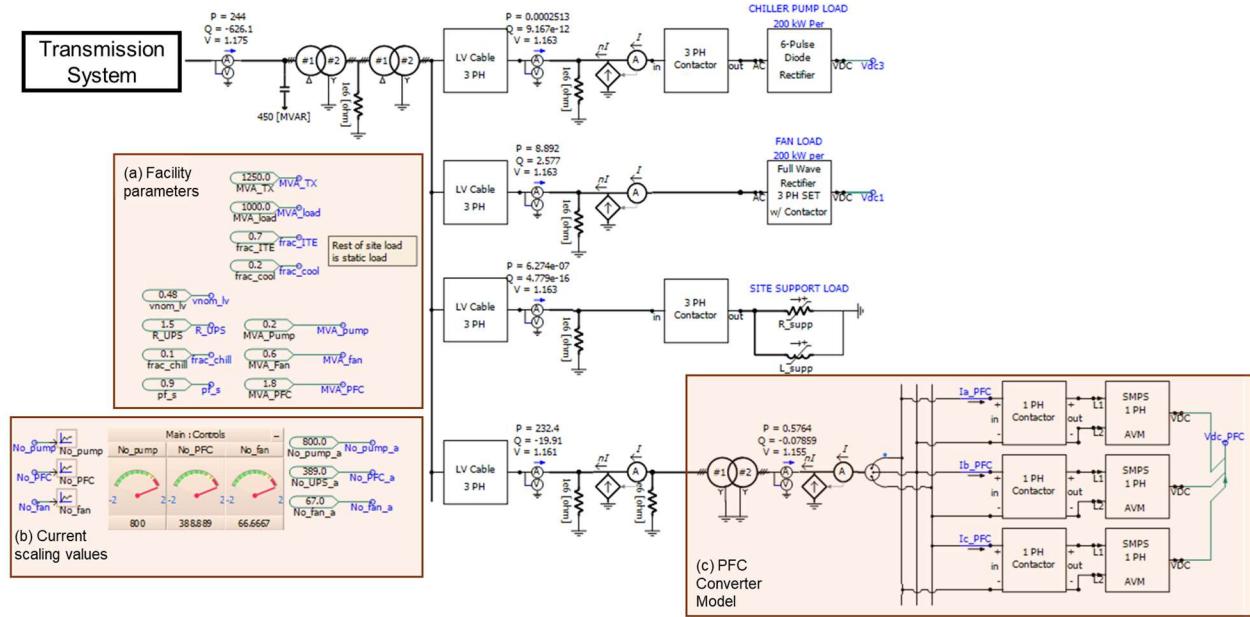

| Figure 38: Overview of simple data center model.....                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 50 |

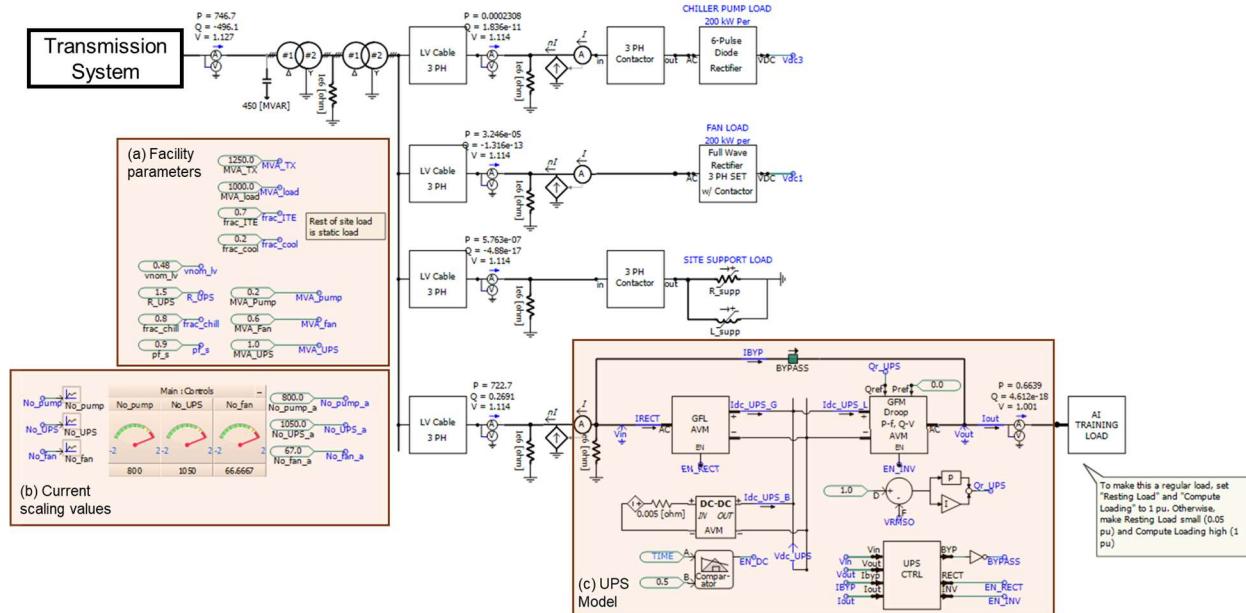

| Figure 39: Overview of data center model with centralized UPS.....                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 51 |

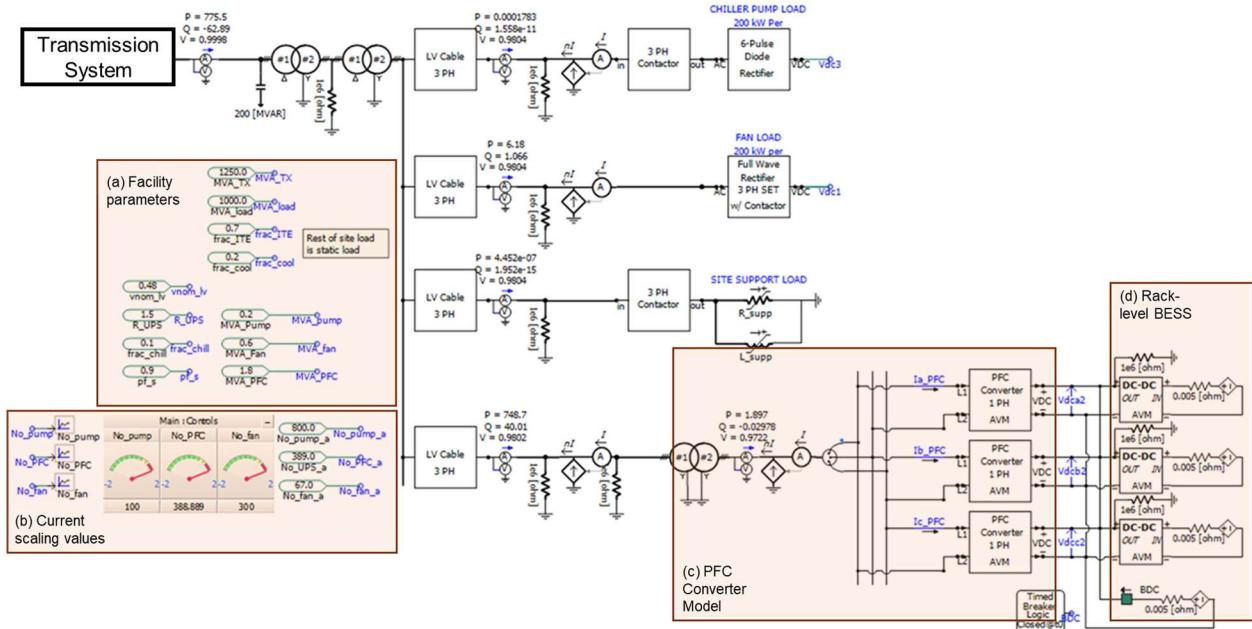

| Figure 40: Overview of data center model with distributed UPS.....                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 53 |

| Figure 41: Icon (left) and main electrical schematic (right) of <code>DC.bi.avm</code> .....                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 54 |

| Figure 42: Icon (left) and main hardware schematic (right) for <code>DC.bi.swm</code> component.....                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 55 |

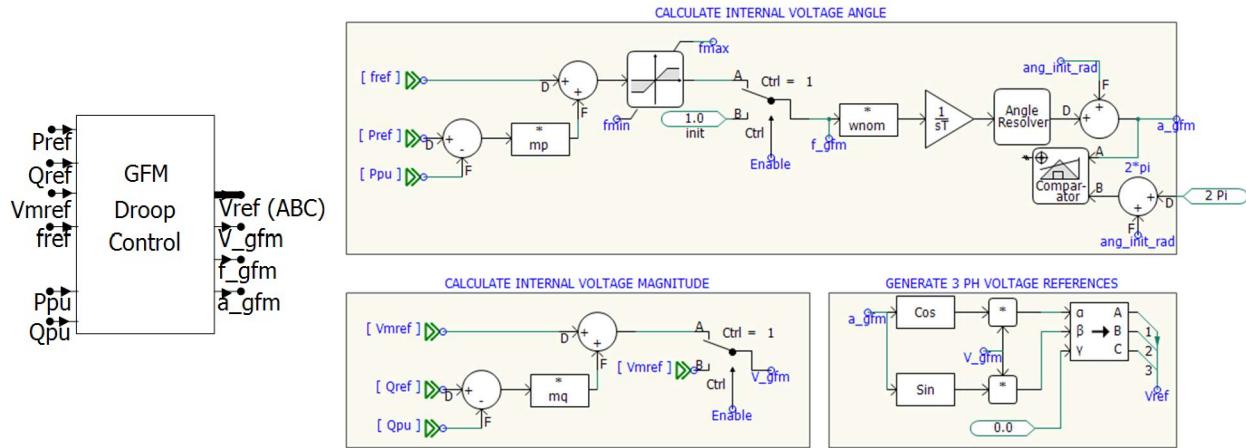

| Figure 43: Icon (left) and main control elements (right) for the <code>gfm_droop</code> component.....                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 56 |

| Figure 44: Icon (left) and main control diagram (right) for <code>gfm_droop_vdc</code> component.....                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 57 |

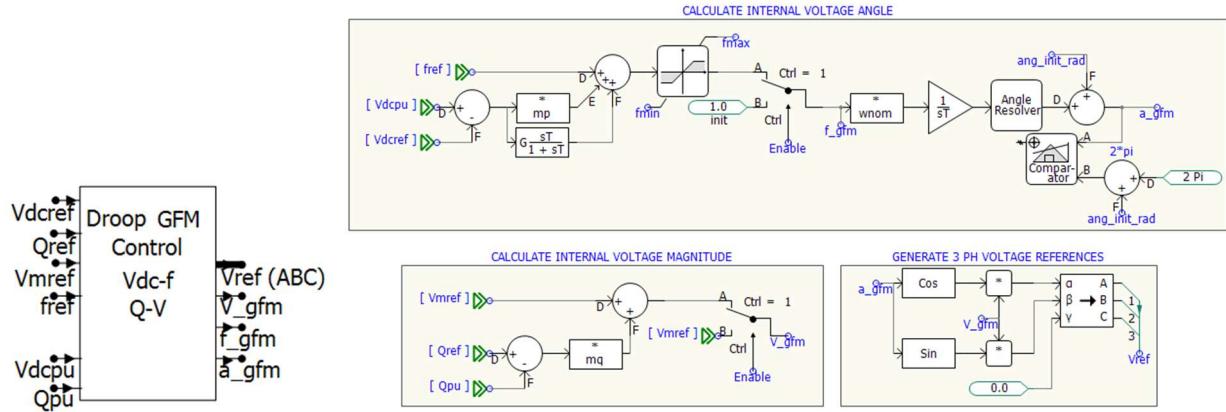

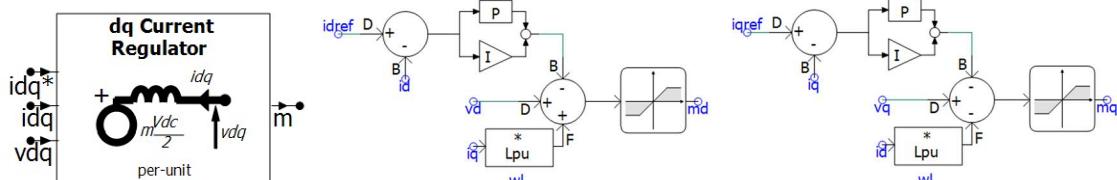

| Figure 45: Icon (left) and main controls (center, right) for the <code>ireg</code> component .....                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 58 |

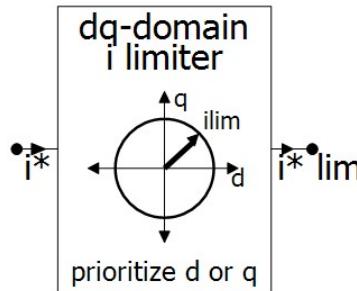

| Figure 46: Icon for the <code>ilim_dq</code> component.....                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 58 |

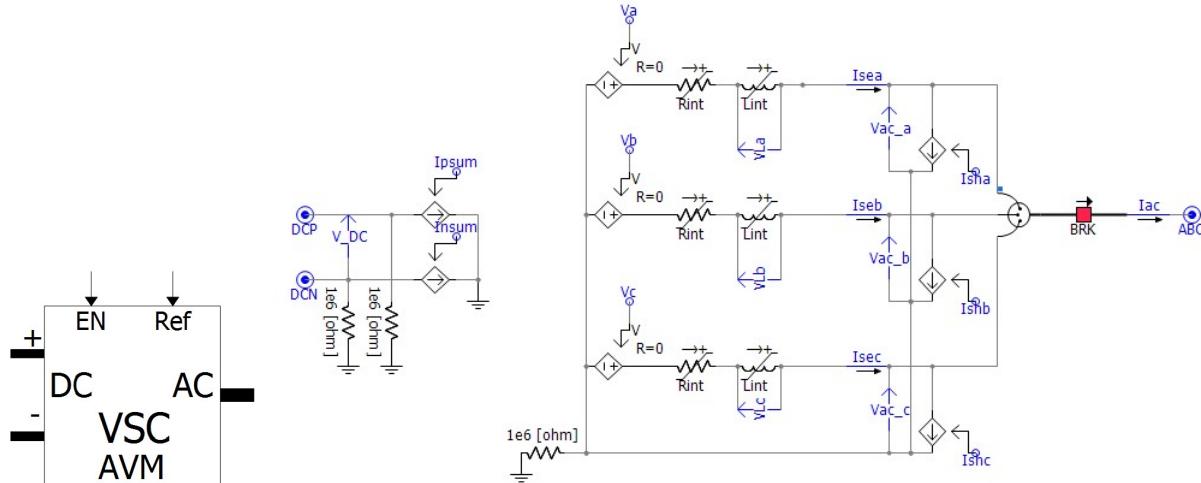

| Figure 47: Icon (left) and main hardware schematic (right) for <code>inv.avm</code> component .....                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 59 |

| Figure 48: Main hardware schematic and major control elements for <code>gfl_inv</code> .....                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 60 |

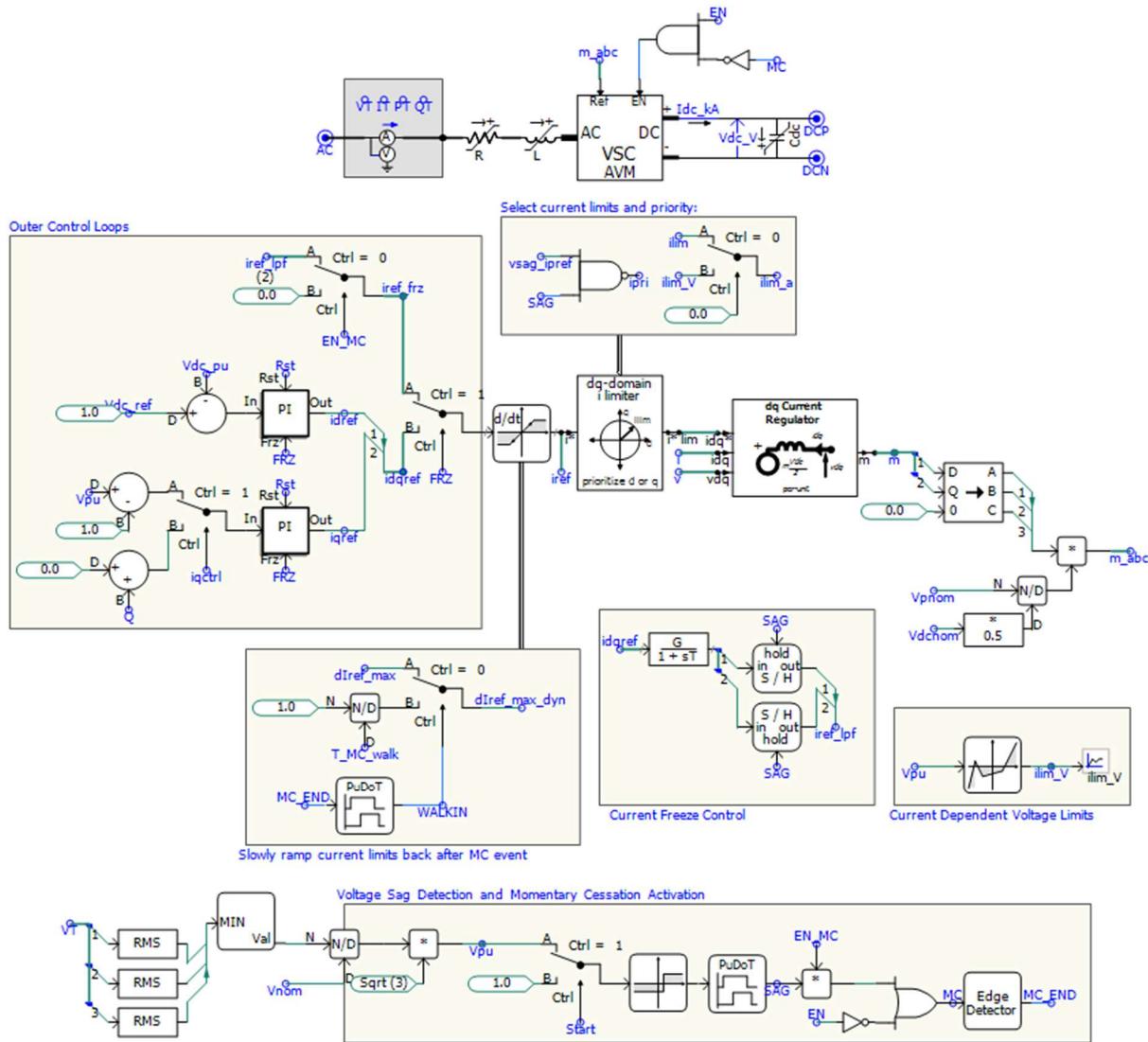

| Figure 49: Hardware schematic (top) and major control features (bottom four rectangles) for <code>inv.gfm_droop.avm</code> component.....                                                                                                                                                                                                                                                                                                                                                                                                                 | 63 |

| Figure 50: Icon (left) and main hardware schematic (right) for <code>inv.swm</code> .....                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 65 |

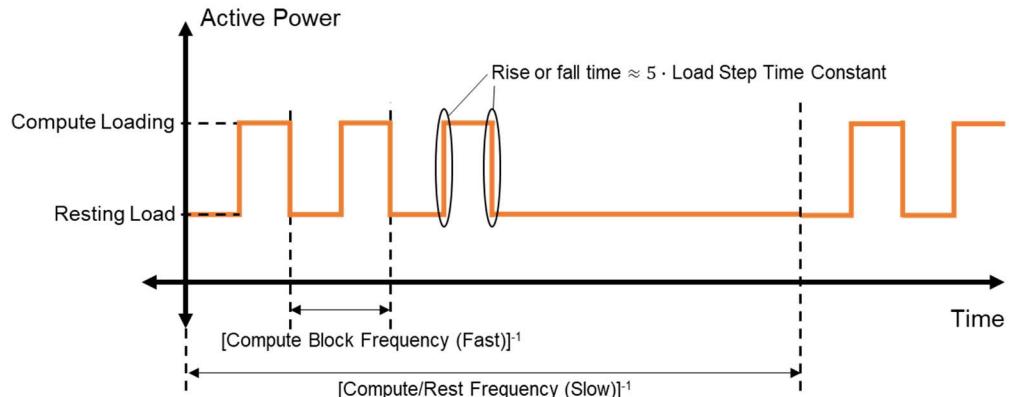

| Figure 51: Simplified AI training waveform and relationship with <code>load.ai_train</code> component parameters.....                                                                                                                                                                                                                                                                                                                                                                                                                                     | 66 |

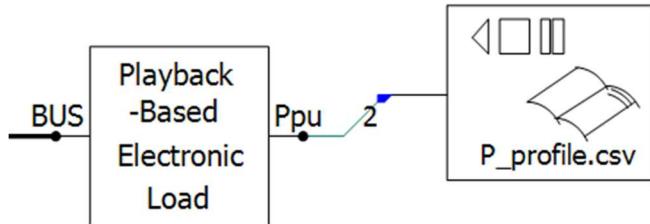

| Figure 52: Icon for <code>load_playback</code> component and intended connectivity with PSCAD's File Read component .....                                                                                                                                                                                                                                                                                                                                                                                                                                 | 67 |

| Figure 53: Recommended parameters for File Read component for use with <code>load_playback</code> .....                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 67 |

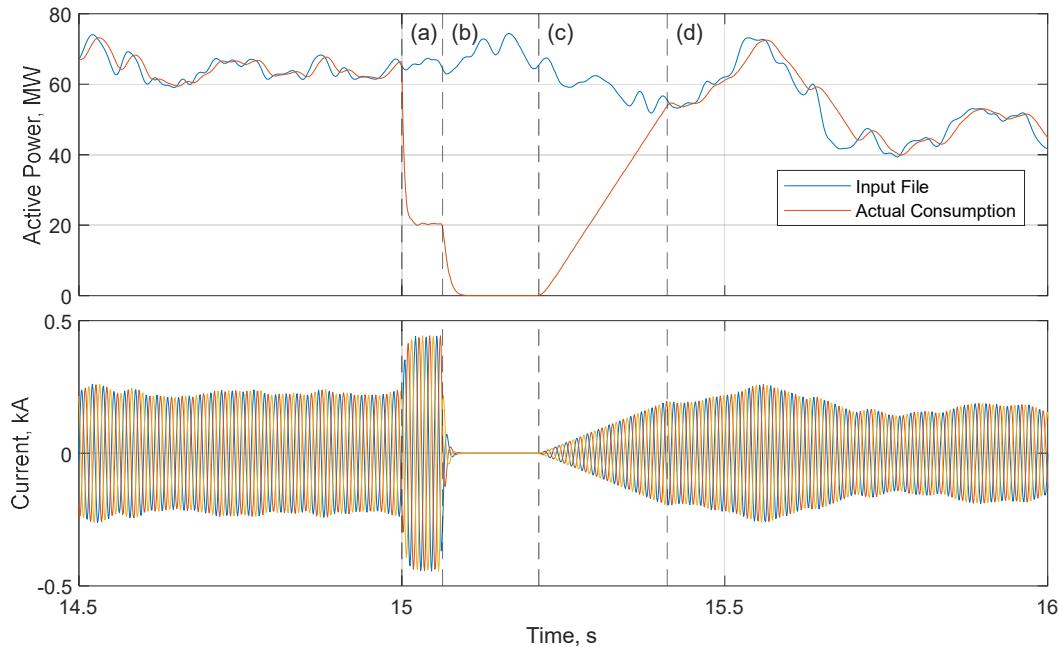

| Figure 54: Exemplar response of <code>load_playback</code> component to close-in 3 PH fault initiated at $t = 15$ s and cleared at $t = 15.1$ s. Active power consumption dips at time (a) as the load current is maintained within the specified limit of roughly 400 A. At time (b), the <code>load_playback</code> component enters momentary cessation and at time (c), which is shortly after the fault is cleared, exits momentary cessation. The ramp rate of the returning load current is also limited and ramping terminates at time (d). ..... | 68 |

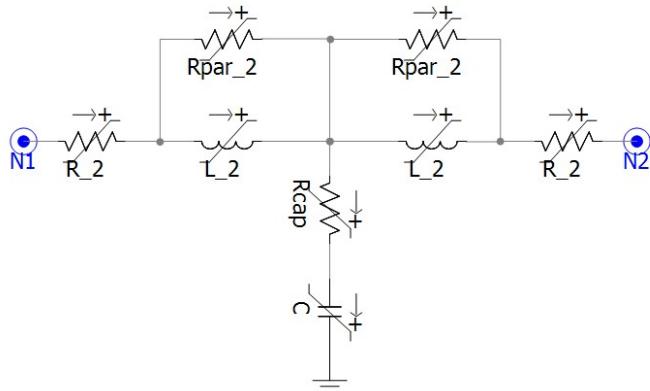

| Figure 55: Topology of <code>LV_cable_3PH</code> .....                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 70 |

| Figure 56: Main hardware schematic for <code>pfc.avm</code> .....                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 71 |

| Figure 57: Icon (left) and main hardware schematic (right) for <code>pfc.swm</code> .....                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 72 |

| Figure 58: Icon (left) and main control diagram (right) for <code>PI_AntiWindUp</code> component.....                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 74 |

| Figure 59: Icon for the <code>PQ_dq</code> component.....                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 74 |

| Figure 60: Icon for the <code>pu_bases</code> component.....                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 75 |

| Figure 61: Icon (left) and electrical schematic (right) for <code>rect_3x_full_wave</code> component .....                                                                                                                                                                                                                                                                                                                                                                                                                                                | 76 |

| Figure 62: Icon (left) and electrical schematic (right) for <code>rect_3x_full_wave_c</code> component .....                                                                                                                                                                                                                                                                                                                                                                                                                                              | 77 |

| Figure 63: Icon (left) and electrical schematic (right) for <code>rect_six_pulse</code> component.....                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 77 |

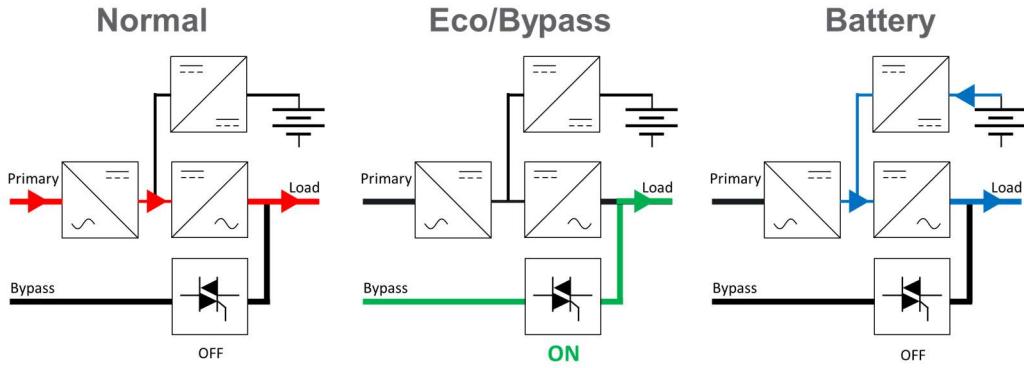

| Figure 64: UPS operating modes and corresponding power flow paths [63].....                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 79 |

| Figure 65: Icon for the <code>ups_ctrl</code> component.....                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 80 |

|                                                                                                   |    |

|---------------------------------------------------------------------------------------------------|----|

| Figure 66: Icon for the <code>uv_sw</code> component.....                                         | 81 |

| Figure 67: Icon (left) and electrical schematic (right) for <code>uv_sw_1PH</code> component..... | 82 |

| Figure 68: Icon for <code>v_reg</code> .....                                                      | 83 |

## Tables

|                                                                                              |    |

|----------------------------------------------------------------------------------------------|----|

| Table 1: Data center designs and their application and grid interface.....                   | 7  |

| Table 2: Kinds of Oscillatory Interactions Data Centers Could Contribute to. ....            | 16 |

| Table 3: Complete Power Electronic Device Models included in the DML.....                    | 23 |

| Table 4: Control algorithm components included in the DML.....                               | 23 |

| Table 5: Grid components included in the DML.....                                            | 24 |

| Table 6: Load profile components included in the DML .....                                   | 24 |

| Table 7: Power electronics hardware components included in the DML.....                      | 24 |

| Table 8: Protection system components included in the DML .....                              | 25 |

| Table 9: Signal processing components included in the DML.....                               | 25 |

| Table 10: Facility parameters for simple data center.....                                    | 50 |

| Table 11: Facility parameters for data center with centralized UPS.....                      | 52 |

| Table 12: Facility parameters for distributed UPS data center.....                           | 53 |

| Table 13: Input parameters for <code>DC_bi_avm</code> component. ....                        | 55 |

| Table 14: Input parameters for <code>gfm_droop</code> component. ....                        | 56 |

| Table 15: Input parameters for <code>gfm_droop_vdc</code> component.....                     | 57 |

| Table 16: Input parameters for <code>ireq</code> component.....                              | 58 |

| Table 17: Input parameters for <code>ilim_dq</code> component.....                           | 58 |

| Table 18: Input parameters for <code>inv_avm</code> component.....                           | 59 |

| Table 19: Ratings-related input parameters for <code>gfl_inv</code> component. ....          | 61 |

| Table 20: Controller-related input parameters for <code>gfl_ibr</code> component.....        | 62 |

| Table 21: Ratings-related input parameters for <code>inv_gfm_droop_avm</code> component..... | 64 |

| Table 22: Control-related input parameters for <code>inv_gfm_droop_avm</code> component..... | 64 |

| Table 23: Input parameters for <code>load_ai_train</code> component.....                     | 66 |

| Table 24: Input parameters for <code>load_playback</code> component.....                     | 69 |

| Table 25: Input parameters for <code>LV_cable_3PH</code> component.....                      | 70 |

| Table 26: Device rating parameters for <code>pfc_avm</code> component.....                   | 71 |

| Table 27: Controller setting parameters for <code>pfc_avm</code> component.....              | 71 |

| Table 28: Protection setting parameters for <code>pfc_avm</code> component. ....             | 72 |

| Table 29: Input parameters for <code>pfc_swm</code> component.....                           | 73 |

| Table 30: Input parameters for <code>PI_AntiWindUp</code> component. ....                    | 74 |

| Table 31: Input parameters for <code>PQ_dq</code> component.....                             | 74 |

| Table 32: Input parameters for <code>rect_3x_full_wave</code> component.....                 | 76 |

|                                                                                            |    |

|--------------------------------------------------------------------------------------------|----|

| Table 33: Input parameters for <code>rect_six_pulse</code> component.....                  | 78 |

| Table 34: Correspondence of UPS controller operating modes to rectifier/bypass status..... | 79 |

| Table 35: Rating-related parameters for <code>ups_ctrl</code> component.....               | 80 |

| Table 36: Bypass control-related parameters for <code>ups_ctrl</code> component.....       | 80 |

| Table 37: Rectifier protection-related parameters for <code>ups_ctrl</code> component..... | 81 |

| Table 38: Input parameters for <code>uv_sw</code> component.....                           | 82 |

| Table 39: Input parameters for <code>uv_sw_1PH</code> component.....                       | 83 |

| Table 40: Input parameters for <code>ireq</code> component.....                            | 83 |

## 1.0 Introduction

In recent years, the energy consumption patterns of data centers have grown considerably in magnitude and complexity, resulting in substantial consequences for the operation of the power grid at large. Grid planners and operators need models in order to proactively evaluate the effects of interconnecting data centers on the grid. These evaluations can be used to determine the performance restrictions and technical solutions necessary for reliable integration of data centers.

Many studies must be performed to evaluate grid impacts from a large data center, and different kinds of studies require different kinds of models. Of the many kinds of models needed, this work's focus is on electromagnetic transient (EMT) modeling of data centers. EMT modeling is one of the highest-fidelity forms of modeling used in power system analysis and significant expertise and technical data is required to construct a reasonable EMT model. The purpose of this work is to accelerate industry's ability to develop suitable EMT models of data centers.

Pacific Northwest National Laboratory (PNNL) has developed a library of generic EMT models, referred to as the data center modeling library (DML), using the power systems computer-aided design (PSCAD), a tool widely used in industry to simulate electromagnetic transients in power systems. The DML has been made freely available and most of this report is dedicated to explaining how DML was developed and how it may be used productively. The models in DML are intended for studying the aggregate effects of data center components on the power grid; they are of limited use for studying design problems or disturbances within the data center itself.

The DML is not a realistic representation of any one data center, nor is it intended to be. Rather, it is a reasonable starting point for the development of site-specific models for use in grid-level studies. Site-specific models must be developed using subject-matter expertise and site-specific technical data. A wide range of common data center components have been implemented along with organizational features intended to reduce the additional labor needed to make the models site specific. Lessons learned, typical design practices, and opportunities for simplification have been documented to aid engineers in managing the potentially impractical level of complexity involved in EMT model development.

This report's contents are organized as follows. Section 2.0 describes the design of power systems used within data centers and presents six aggregated site models which can be used to represent most modern or near-future data centers. Section 3.0 discusses practices for EMT modeling of data centers, explaining the situations in which it is beneficial to undertake the time-consuming process of performing an EMT study and the kinds of risks and challenges such a study can articulate. Section 4.0 describes in detail how the different components of data center power systems can be represented in an EMT model and how this relates to the components provided in DML. Section 5.0 describes the power system models included in DML and documents their functionality. Section 6.0 documents the functionality of the individual component models included in DML.

## 2.0 Data center Power Systems

The purpose of this section is to provide a succinct overview of those aspects of data center power systems that are most relevant for grid level dynamic studies. This highlights the major components needing representation in various studies and outlines current and near-future archetypes for data center design.

### 2.1 Power Electronics Topologies

Most grid-level EMT studies involving data centers employ relatively simple representations of the site distribution systems, with most of the model fidelity being concentrated on the power electronics that support information technology equipment (ITE). The power electronic architectures for most data centers fit into one of six designs—these are described below, and single-line diagrams of the proposed aggregated EMT models are provided. The first three designs are in use today and case files for them are included in DML. The later designs range from near future (e.g., within 2 years) to futuristic (e.g., within 10 years) and the alpha release of DML does not include all of the component models required to represent these systems. A more detailed discussion of the reasoning behind selecting the specific components shown within the single-line diagrams may be found in Section 4.0.

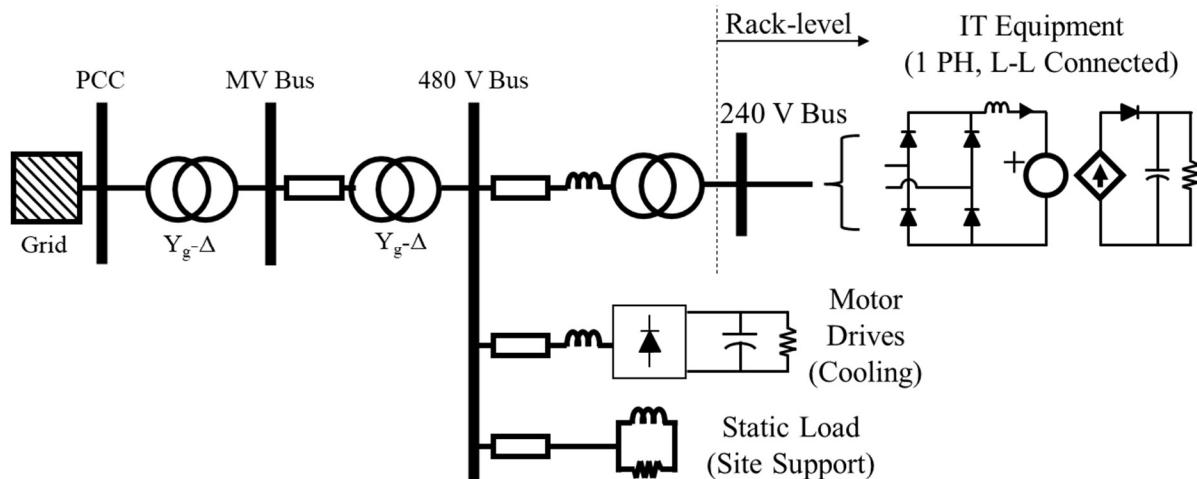

#### Design 1: Simple

The simple data center design is primarily associated with cryptomining operations and seldom used for other applications (Figure 1). Compared to most other data centers, reliability is less critical and the costs associated with the electric plant are more influential on the site's economic viability. AC/DC conversion at the rack level is done at 240 V and diode-based power factor correction (PFC) converters are used. No uninterruptible power supply (UPS) or on-site backup generation is present.

Figure 1: Single Line Diagram of Simple Data Center Design.

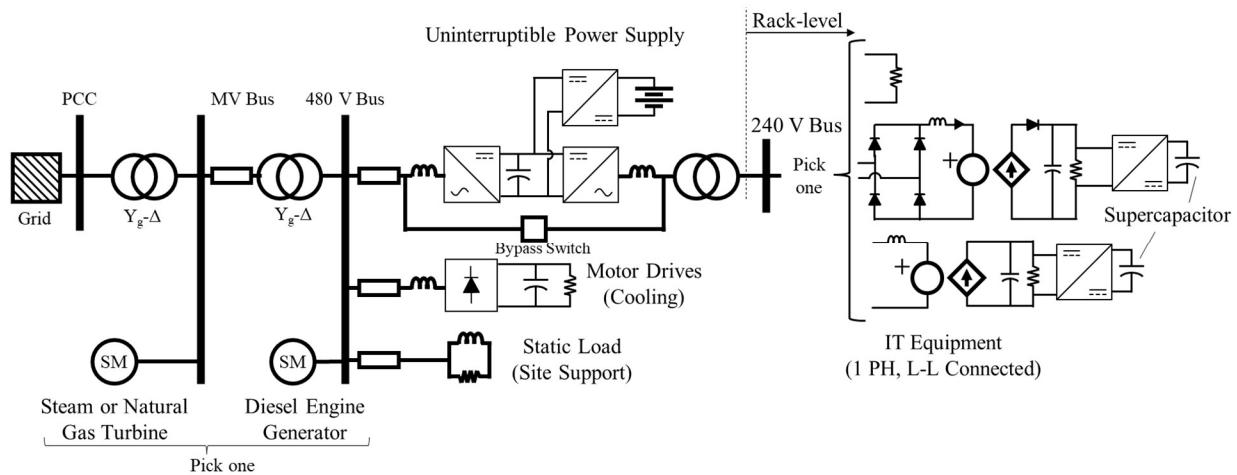

#### Design 2: Centralized UPS

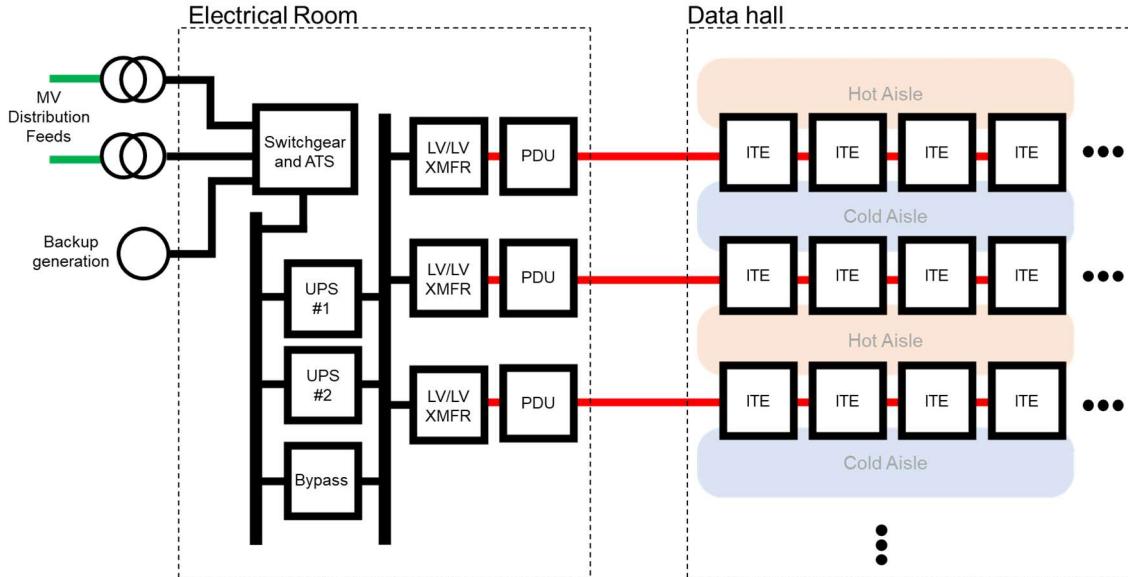

The centralized UPS design is likely the most common for many data centers currently in operation (Figure 2). ITE is located behind large (~1 MVA each) three-phase UPS to protect it

from grid disturbances and ensure continuity of service in the event that the data center must disconnect from the grid and start up local backup generators. While not considered in grid-level studies, high voltage (HV) and medium voltage (MV) systems are equipped with numerous alternate feeds and automatic transfer schemes. Data centers of this design are often designed for concurrent maintainability and achieve Tier 3 reliability as defined by the Uptime Institute [1]. On-site generation is provided and consists of either distributed diesel engines or large steam or natural gas turbines. Traditionally, these are never paralleled with the grid and are only used after the data center has disconnected from the grid following a disturbance. The UPS batteries are used to supply the load in the interim period. However, a recent trend has been for on-site generation to become part of the grid's generation pool and to provide occasional support in order to manage grid-level generation shortages or transmission congestion.

Figure 2: Single Line Diagram for Centralized UPS Data Center Design.

A single UPS serves a number of IT racks, with modern per-rack power demands typically in the tens of kilowatts for traditional applications and over 100 kilowatts for high-performance computing (i.e., AI training) applications. The rack level power supplies may be modeled as a simple resistive load (potentially with a time-varying demand) unless the UPS is operated with the bypass switch closed. Single phase power supplies are represented in Figure 2 using the average-value model (AVM) for both unidirectional (diodes shown) and bidirectional (no diodes shown) models for a voltage-source converter to illustrate that either may be used. More detail on this is given in Section 4.1.

There are many variations on the centralized UPS design on a site-to-site basis. Some or all of the cooling load at a site may be behind UPS as well—this is increasingly common in artificial intelligence (AI) applications as high heat densities and hardware costs make the risks associated with temporary cooling interruptions more significant. Some of the motor load may consist of line-connected induction motors rather than motor drives.

Supercapacitors at the rack level are newly come to market [2] and are present at few sites at the time of writing. Their primary application is smoothing of rapid changes in compute load (e.g., due to hyperscale AI training) in order to reduce both site- and grid-level disruptions. However, they may also come to be utilized to improve the site's ride-through capabilities as well.

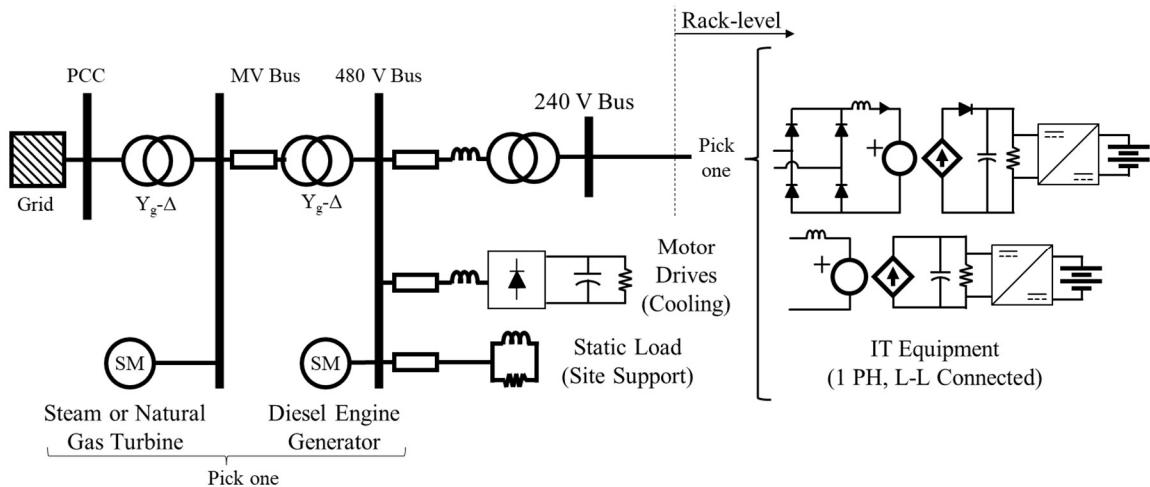

### Design 3: Distributed UPS

The distributed UPS design philosophy is used for some new data centers; Meta is a notable adopter of this design [3] [4] [5]. Battery backup and support of the IT load is achieved using rack-level storage, meaning that the UPS function is distributed at the rack-level. This results in significant cost savings owing to the lack of double conversion UPS but does result in information technology (IT) load being exposed to power quality disturbances such as voltage excursions and harmonics. Whether or not this meaningfully affects site reliability will depend on local power quality conditions and the design of site-level protection and automation schemes.

Figure 3: Single Line Diagram of Distributed UPS Data Center Design.

Backup generation at distributed UPS sites is operated in a manner similar to that at centralized UPS sites; the data center disconnects in response to grid disturbances that threaten process reliability, rack-level batteries provide continuity of power for IT loads, and local generation is rapidly brought online to serve the load.

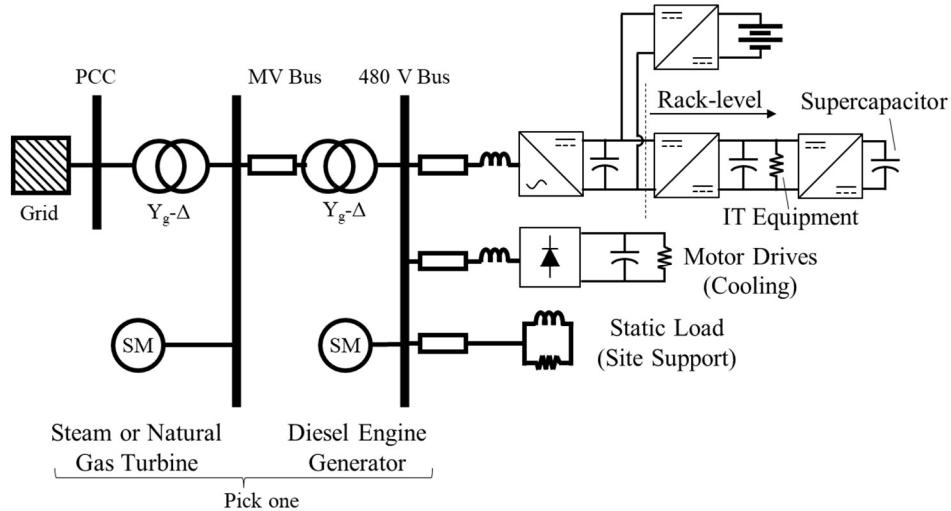

### Design 4: Low-Voltage DC Distribution

The remaining three designs are based on DC distributions and are major R&D foci for data center suppliers [6] [7] [8] [9] [10]. The technical benefits for adopting DC distribution in power electronics-rich environments have long been recognized in research [11] and have even seen nascent industry interest in the past [12] [13], but high costs and low supply chain maturity have slowed adoption. The unique requirements and resources of hyperscale AI data center developers have altered this paradigm.

Increased power density needs of AI platforms are the primary motivation for original equipment manufacturers (OEMs) and data center developers to expend significant capital on developing DC distribution systems—present-day graphics processing unit (GPU) racks attain 120 kW, and prototypes up to 1 MW have been developed and planned for 2027 [10] [7]. Training larger and more sophisticated AI models requires more compute resources, and a high degree of low-latency connectivity between individual processors is required for good performance during training. The latency and bandwidth constraints this introduces make it prohibitive to continue spreading compute resources over a wider area, and the result is a strong demand for the high power densities which only DC power systems can provide.

The low voltage DC (LVDC)<sup>1</sup> distribution design is a central R&D focus for many OEMs [6] [14] and is in the prototype stage (Figure 4). It is also seen as somewhat of a stepping stone to the later two architectures, which require additional R&D and field experience with operating DC distribution systems. From an aggregated perspective, this design may be viewed as a variation of the centralized UPS design wherein the output inverter is absent and the DC link voltage (either 400 V or 800 V, depending on the vendor [10] [15]) is distributed directly to individual racks of IT equipment. The design of the 480 V rectifiers will likely be similar to those employed in double-conversion UPS today. The rack-level power supplies are no longer single-phase AC/DC converters but rather DC/DC converters which step the 800/400 VDC down to 50 VDC for ITE to use.

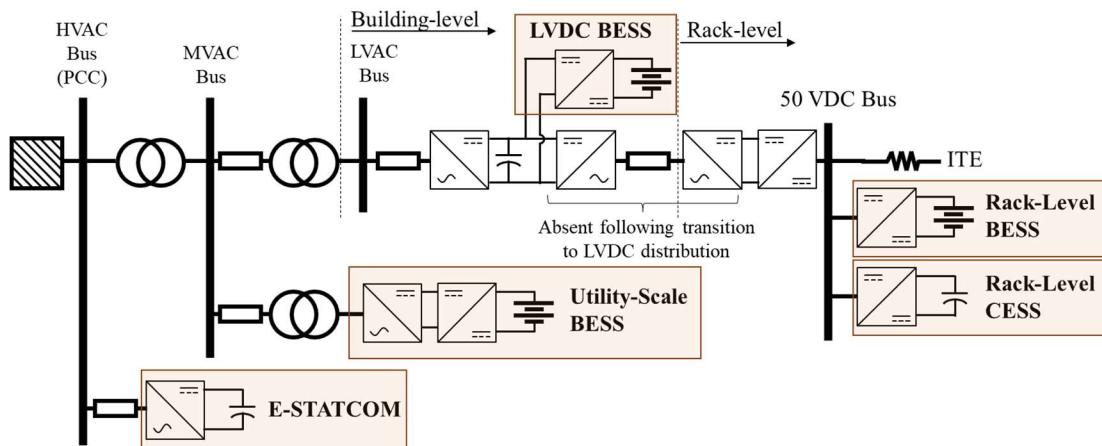

Figure 4: Single Line Diagram of Low-Voltage DC Distribution Design.

Much like in a double-conversion UPS, a battery system is integrated at the 400/800 VDC level. The battery backup may be used for load smoothing, grid support, ride-through, backup power, or a mix of all three. Supercapacitors at the rack level may also be used for load smoothing, which could reduce the necessary battery capacity and/or extend battery lifetime. Batteries could also be installed at the rack level, as is done in the distributed UPS design. On-site inverter-based generation may also be connected to the LVDC network (rather than through its own set of AC/DC converters and step-up transformer). This could reduce losses and capital costs but may introduce operational complexities and reliability concerns relating to shared points of failure.

In principle, the motor drive rectifiers could also be eliminated by supplying the drive inverters directly from the LVDC distribution. However, rectifiers for drives are not necessarily major drivers for site-level cost or limitations. Commercial drive rectifiers may not be compatible with the DC supply conditions provided by the LVDC network, and otherwise beneficial drive features such as flying restart may become a source of complexity. Still, potential benefits from making the inertia of cooling motors available as a form of short-term energy storage (and savings in the form of reduced rectifier capacity and DC link capacitance) are worth further investigation.

<sup>1</sup>Here, we use the term LVDC distribution to refer to distribution at DC voltages ranging from 600 to 4000 VDC. In datacenter industry literature, this is often referred to as HVDC. In this report, we delineate LV, MV, and HV levels within the context of electric power systems.

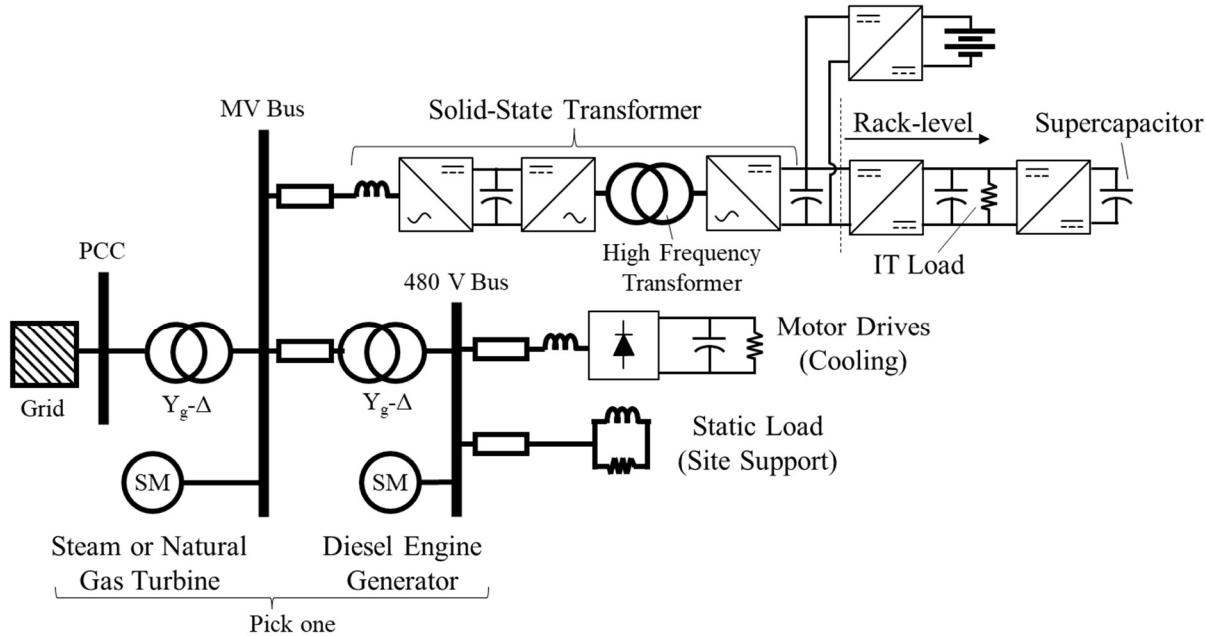

## Design 5: Medium-Voltage Solid-State Transformer

Power density may be further increased beyond the LVDC design by replacing the MV to LV transformers and LVAC cables with a MV AC/DC converter and DC/DC conversion stage to step down the MVDC to LVDC. Solid-state transformer (SST) technology is viewed as a promising solution for achieving these functions (Figure 5).

Figure 5: Single Line Diagram of Medium-Voltage Solid-State Transformer Design.

The SST replaces the MV to LV transformer and its output stage replaces the rack-level AC/DC converter employed in the LVDC distribution design—the SST directly provides the 400 or 800 VDC that is then distributed to the racks. The remaining downstream architecture is similar to the LVDC design. The number of racks that can be supplied with a single SST is uncertain given the ambitious R&D targets set in place for both SST deployment and AI rack power density. With a medium-voltage AC input, economical design of an SST rated for tens of MVA is plausible, meaning that a single SST will likely be able to serve more racks than the LV rectifier used in the LVDC distribution design.

For both the LVDC distribution and MVDC SST designs, improving the LVDC voltage to above 1 kV (e.g., 1.5 kVDC) has been identified as an R&D target. While this may require significant product development and improvements to personnel safety measures, the resultant changes from the perspective of EMT modeling may not significantly affect the aggregated model to be used.

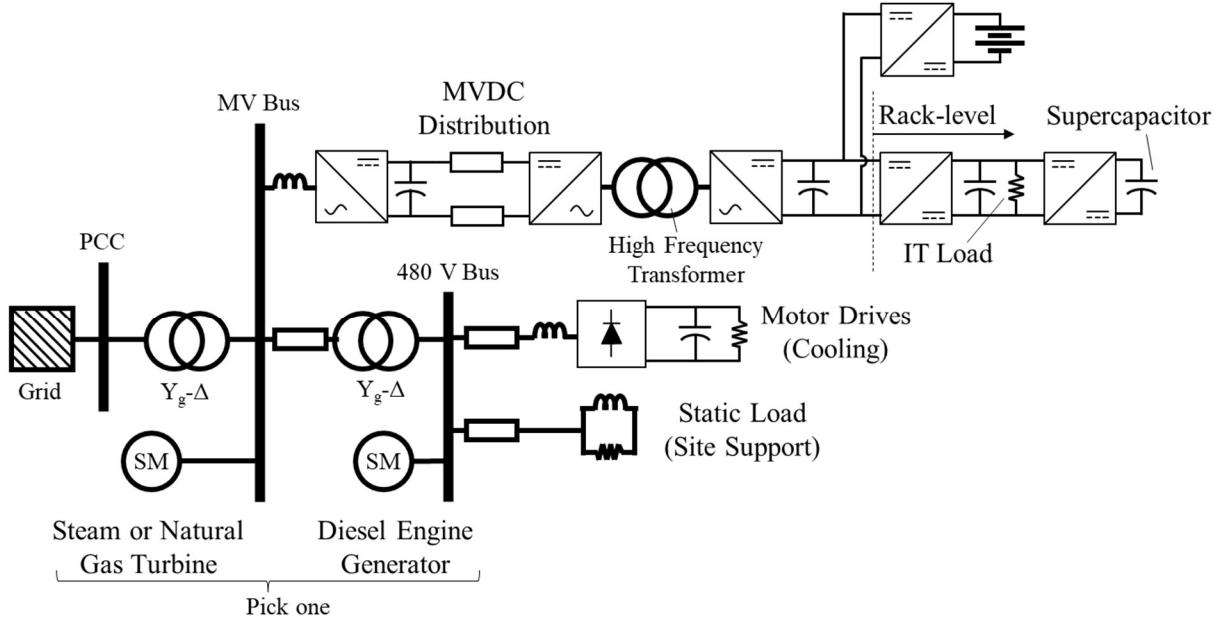

## Design 6: Medium-Voltage DC Distribution

The MVDC distribution design is the logical next step from the MVDC SST design—power density may be further increased by replacing the MVAC distribution with an MVDC distribution system (Figure 6). In terms of the scope of product development required, the MVDC design is a significant step involving cables, busbars, switchgear, circuit breakers, etc. to a much greater extent than in the LVDC distribution or MVDC SST designs. Thus, while data center suppliers

expect to begin deploying the LVDC and SST technologies in the field within the next several years, MVDC-based data centers are likely further away from seeing field service.

Figure 6: Single Line Diagram of Medium Voltage DC Distribution Design.

Observe that, from an aggregate modeling perspective, this is not radically different from the MV SST design—the primary difference is that the MV cable is now located after the MV AC/DC conversion stage; a high frequency transformer is still likely to serve as an attractive option for reducing MVDC to LVDC for rack-level distribution.

Table 1 summarizes the six data center designs introduced. Observe that evolution in data center power electronics is being driven by AI hyperscalers, and that future designs are trending towards the use of a 3 phase (PH) active front-end design, similar to that used in inverter-based resources (IBRs).

Table 1: Data center designs and their application and grid interface.

| Design               | Primary Application                 | ITE Grid Interface      |

|----------------------|-------------------------------------|-------------------------|

| 1: Simple            | Cryptomining                        | 1 PH ITE Power Supplies |

| 2: Centralized UPS   | Modern data centers                 | 3 PH active rectifier   |

| 3: Distributed UPS   | Modern data centers                 | 1 PH ITE Power Supplies |

| 4: LVDC Distribution | Near-future (<5 yr) AI hyperscalers | 3 PH active rectifier   |

| 5: MV SST            | Near-future (<5 yr) AI hyperscalers | 3 PH active rectifier   |

| 6: MVDC Distribution | Future (>5 yr) AI hyperscalers      | 3 PH active rectifier   |

For grid level studies, further simplifications of all these architectures may be possible—many grid-level studies of power electronics use highly simplified representations of any power conversion stages beyond those directly connected to the grid. In four of the six designs considered, the ITE equipment is interfaced with the grid via a 3-phase converter with energy storage. Further study and development of these converters may allow for existing modeling approaches for IBRs to be heavily utilized for representing data centers in grid-level studies. Early-stage performance requirements for large loads [16] [17] are similar in many respects to

IBR performance requirements, such as those in IEEE Std 2800 [18] and NERC PRC-029-1 [19].

Aside from emergent grid integration issues such as ride-through, designs 2 and 3 are highly mature from the data center perspective. Many data centers have highly stable electricity demand and use few or none of the high-power AI racks which are driving the power density requirements and investment in DC distribution systems. In such cases, designs 2 and 3 are attractive options, especially when reliability is paramount and thus appetite for less proven technology is lower. Thus, it is expected that these designs will continue to be used in a significant fraction of new data centers for the foreseeable future.

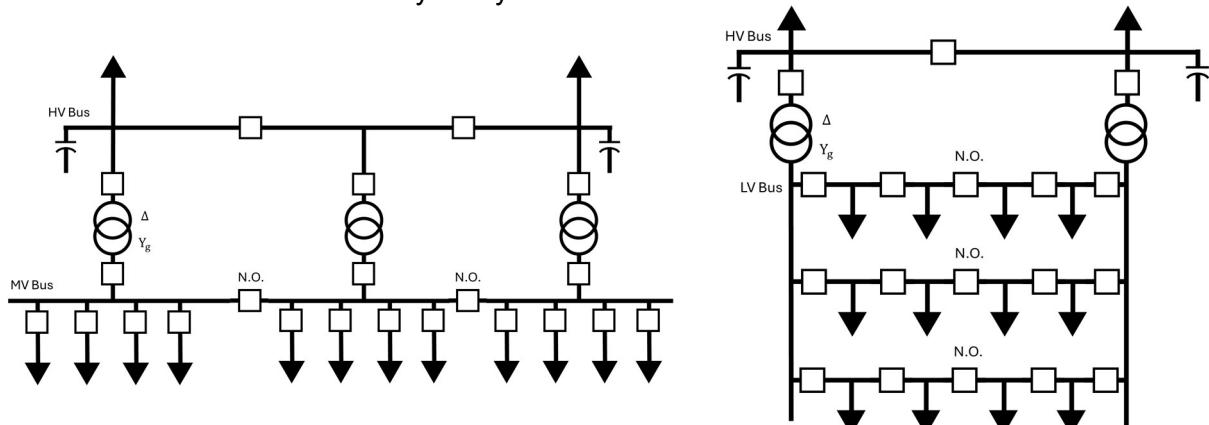

## 2.2 Balance of Plant

In Section 2.1, the topology of the HV, MV, and LV networks has been highly simplified in accordance with the DML's focus on grid-level studies. In this section, a brief description of AC HV, MV, LV networks in data centers is given so that DML users may be somewhat familiar with the detailed topologies that aggregated models are based on.

Generally speaking, the HV and MV power systems employed in large data centers are similar to those used in mission-critical industrial facilities or urban areas—numerous redundancies and alternate feeds are provided to accommodate faults and equipment outages. Space saving measures such as high-density substation layouts and switchgear are employed. Figure 7 illustrates two HV substation layouts sometimes used in data centers. These layouts are similar to distribution substations used by many utilities.

Figure 7: Exemplar substation layouts for data center HV substations.

The protection and control of these substations is also similar to typical utility practices; transformers and busbars are protected from faults using current differential protection. Short feeders may be protected either via time-inverse overcurrent or current differential. Large power transformers are equipped with mechanical protections and gas monitoring, and switchgear is equipped with arc flash protection.

Fast bus transfer schemes and networked distribution systems are less common as the UPS provide continuity of service to critical loads, reducing the need for the protection system to perform high-speed fault clearing or reconfiguration. That said, both automatic and manual reconfiguration schemes are widely used to ensure continuity of service even in the event of multiple outages or failures.

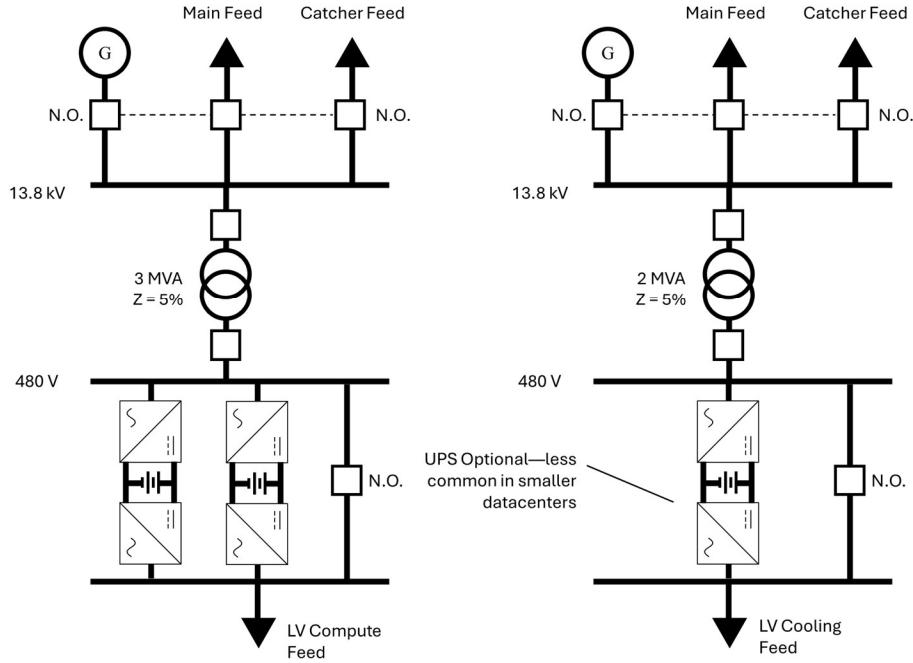

At the LV level, large data centers are often constructed by repeated “blocks” each rated for several megawatts each (Figure 8). Each block generally may be fed by two different MV feeds and, if backup generation is distributed (as is often the case), backup generation is connected (either at the MV or LV level). UPS are employed at this stage, often in redundant pairs and with each carrying a portion of the total load. In grid-level EMT studies, these UPS may be combined into a larger equivalent (this is the approach used in the DML examples). Cooling blocks also use UPS in larger data centers; the tolerance for cooling interruptions in hyperscale data centers is ever-decreasing as racks operate at higher power densities.

Compute Block – 2.5 MW each.      Cooling Block – 1.5 MW each.

Figure 8: Single Line Diagrams for Medium-Voltage Compute and Cooling Blocks.

The low-voltage distribution equipment is then usually located within a dedicated electrical room located adjacent to the data hall where the ITE is located. Figure 9 illustrates the basic connectivity and arrangement of LV distribution equipment in relation to the data hall.

Figure 9: Simplified Layout of LV Electrical Distribution within Data Hall.

Power distribution units (PDUs) serve as switchboards for the LV cables feeding racks and are the primary means for monitoring and automation of power distribution at the rack level. PDUs range in functionality from basic high-quality power strips to automation and control platforms that provide high-fidelity monitoring and aggregation of a variety of electrical and mechanical sensory data from within the data hall. Thus, while PDU are a critical component of the site-level operations and monitoring, their relevance to grid-level EMT studies is limited.

Figure 10 and Figure 11 illustrate typical arrangements and installation conditions for LV distribution equipment in the utility room of a modern data center. Connections are usually made with cable located in metal conduit, with incoming feeds usually coming from MV equipment located outdoors and outgoing feeds running to the adjacent data hall. In high-density or space constrained sites, MV equipment may also be located inside.

Figure 10: Electrical Room Housing 28 MW of UPS Capacity [20].

Figure 11: Electrical Room for Medium-Sized Data Center [21].

Figure 12 and Figure 13 illustrate typical installation conditions within the data hall. Most of the floor space is dedicated to ITE racks. Both drop ceiling and raised floor are commonly employed to provide passage for air supplied by cooling-rack air handlers (CRAH), as well as potential passage for power cables, piping for any rack-level cooling, and communications cables.

Overhead raceways provide another path for routing this infrastructure. There are many different practices for how air flow and pipe/cable routing are handled at the data hall level [5].

As first indicated in Figure 9, ITE racks are arranged into rows and organized into hot and cold aisles. Rack-level cooling admits air from cold aisles and emits it into hot aisles; ports for user interactivity are located on the cold side of the rack and any hazardous high-power connections are located on the hot side. Some form of thermal barrier between aisles is generally used, Figure 13 illustrates the application of hot-aisle containment—the areas between aisles are enclosed in transparent panels and heat is exhausted through either the ceiling or floor<sup>1</sup>.

Figure 12: Representative Data Hall [22]. This Facility is Rated for Tens of Megawatts, Tier IV Reliability, and LEED Gold Efficiency.

Figure 13: Representative Data Hall [23]. This Facility uses a High Power Density Design and Features Hot-Aisle Containment.

Figure 14 and Figure 15 illustrate typical installation conditions for the two main sources of cooling load, compute room air handlers (CRAH) (left) and chillers (right). CRAH are located in rooms adjacent to the data hall and provide the data hall with air that is regulated in terms of its temperature, flow rate, humidity, and pollution. The mechanical room usually houses automation controllers and support systems for both air and coolant handling. In large data centers, centralized chilled water plants are the primary method for rejecting heat produced by ITE<sup>2</sup> to the outside environment. Heat exchangers throughout the facility (e.g., with the CRAH and any rack-level liquid cooling) are dedicated to transferring heat away from ITE and into coolant loops that flow through outdoor chillers. In large data centers, plant-scale chillers are typically located on the facility rooftop.

<sup>1</sup>Air flow velocities in data halls are usually too high for heat's natural tendency to rise to be a major design factor [5].

<sup>2</sup>The majority of electricity consumed by ITE is converted into heat. As a result of the thermal performance limitations of modern ITE and cooling systems, coolant temperatures are generally too low to support other processes (e.g., district heating or steam generation) [5]. However, market demands for higher power density are driving adoption of rack-level liquid cooling solutions [92] and high-temperature semiconductors (e.g., SiC and GaN) [93]. These technologies permit higher coolant temperatures which may supply other processes.

Figure 14: Mechanical Room Housing Compute Room Air Handlers (CRAH) [20].

Figure 15: Large Rooftop Chiller Unit for Data Center [20].

The pictured chiller is rated for 345 tons, meaning that the cooling water pump rating is likely about 1.5 MW. Large design margins are used when sizing cooling capacity, so the typical power demand for this chiller is likely to be significantly less than 1.5 MW.

## 3.0 Electromagnetic Transient Modeling of Data centers

In Section 2.0, as part of an overview of data center power systems, we have discussed some simplifications, common practices, and assumptions that may be employed to manage the potentially prohibitive level of detailed modeling involved in EMT modeling of large data centers, which contain tens of thousands of high-power components. As with many practical applications of EMT modeling, a clear understanding of study objectives and a series of pragmatic assumptions is required to complete studies in a reasonable time frame. In this section, we will discuss some potential applications for grid-level EMT modeling of data centers and the kind of EMT models that are suitable for conducting them. This discussion is aimed towards studies that consider the impacts of the data center(s) under study on the grid, rather than studies of site-level issues.

In subsection 3.1, general practices for determining the need and scope of EMT studies for data center interconnection studies are discussed. Subsection 3.2 addresses the applicability of the DML specifically to these studies.

### 3.1 EMT studies for Data center Interconnection

The details of EMT models are tailored to the kinds of study they are used for. In developing the DML, we considered a number of power system studies which might be conducted as a part of the data center interconnection process. The scope of studies discussed here is based on the scope of issues discussed in NERC's recent large load risk assessment [24] as well as a table developed by Electranix [25]. This overview is also informed by ongoing activities within the ESIG Large Loads Task Force and the NERC Load Modeling Working Group, both of which are developing data center modeling guidelines for grid-level studies. These will likely be publicly released in 2026.

Here, data center interconnection studies are organized into three categories: oscillatory interactions, voltage and frequency regulation, and power quality. This list omits studies which are clearly outside the domain of EMT analysis, such as load forecasting or evaluating steady-state capacity limits.

#### 3.1.1 Oscillatory Interactions

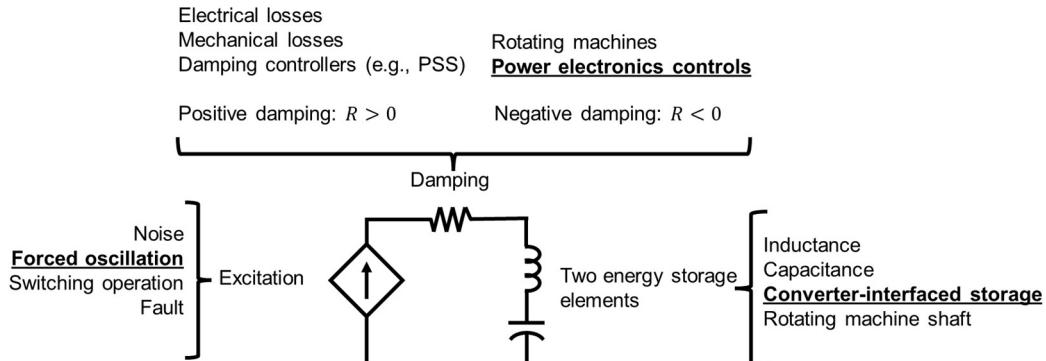

The category of oscillatory interactions encompasses a wide range of scenarios, and the potential role of the data center and related modeling requirements varies. Figure 16 illustrates the essential elements of any oscillatory interaction, along with examples of the grid components and the elements they play a role in. Bolded and underlined items represent the data center components that can contribute to an oscillatory interaction. The current source with a series RLC circuit directly represents a circuit used to study harmonic resonance with shunt capacitors, but it serves as a convenient analog for other forms of oscillatory interaction.

Figure 16: Essential Elements of an Oscillatory Interaction—Excitation, Damping, and at Least Two Energy Storage Elements.

## Energy Storage Elements

Any oscillation involves energy exchange between at least two different forms of energy storage. The frequency of the oscillation is dictated by the time constants associated with the energy storage mechanisms. Purely electrical interactions (as opposed to electromechanical or control interactions) involve capacitors and inductors. Electromechanical interactions involve the kinetic energy stored in the masses of rotating machines. Even in the case of oscillatory interactions involving many devices (e.g., interarea oscillations), the devices involved can usually be lumped into one of two groups (e.g., the northern grid or the southern grid).

## Damping

In the simple model of Figure 16, the energy storage elements are lossless—they exchange energy but do not cause any change in the total energy present in the system at a given time. The damping component represents the energy that is introduced or dissipated as energy flows between the two energy storage components. The total damping is the sum of the contributions from many devices, some of which introduce positive damping (i.e., they absorb energy) and some of which introduce negative damping (i.e., they supply energy). If the total damping is negative, any disturbance, no matter how small will result in instability (hence why “noise” is a valid source of excitation for an oscillatory interaction of concern). If an oscillation is lightly (and positively) damped, then the practical concern is that the oscillations produced by step changes (e.g., switching operations and faults) will be long-lasting and that oscillations produced by continuous inputs (e.g., noise or a forced oscillation) will have a large amplitude at certain locations in the system.

Component losses (e.g., mechanical friction, electrical resistance) are the main source of positive damping in power systems. Active components (e.g., rotating machines and power electronics) can provide either positive or negative damping and often produce a significant quantity of negative damping over some range of subsynchronous frequencies [26] [3] [27] [28]. In a real power system, the total damping is not the simple sum of that from individual elements but rather heavily affected by the network topology. The fact that a particular plant or load has negative damping is not inherently a problem—an individual device or plant may contribute negative damping (large or small) at subsynchronous frequencies and yet have a negligible impact on the total effective damping of a given oscillation<sup>1</sup>.

<sup>1</sup>In a recent Level 2 Alert, NERC has recommended that Transmission Operators should establish design requirements for Large Loads that ensures they are “designed in a way to increase damping of the listed

## Excitation

Excitation introduces energy into the system, causing an oscillation. Its behavior is assumed to be independent of the system damping or dynamics of the energy storage elements, hence its depiction in Figure 16 as an ideal current source. The implementation of the excitation and its underlying assumptions vary based on the kind of interaction of concern:

1. Concerns that the net damping of a power system mode may be too low—in this case, the excitation may be a simple test signal, or methods which neglect excitation entirely (e.g., the use of transfer functions) may be employed.

2. Concerns that forced oscillations may attain high amplitudes (e.g., within a turbine shaft) and/or travel significant distances (e.g., due to the coincidence of the forced oscillation frequency with an interarea mode).

3. Concerns that intermittent disturbances may cause long-lasting oscillations

In practice, grid-level studies frequently make use of EMT simulation for (1), as this tends to be a less time-consuming approach to quickly screen for issues.

---

mode shapes for known power system oscillations” [94]. The majority of loads and generators connected to the power system do not and cannot meet this criteria—many will, theoretically, decrease the damping of subsynchronous modes. However, the effects are insignificant in the overwhelming majority of cases.

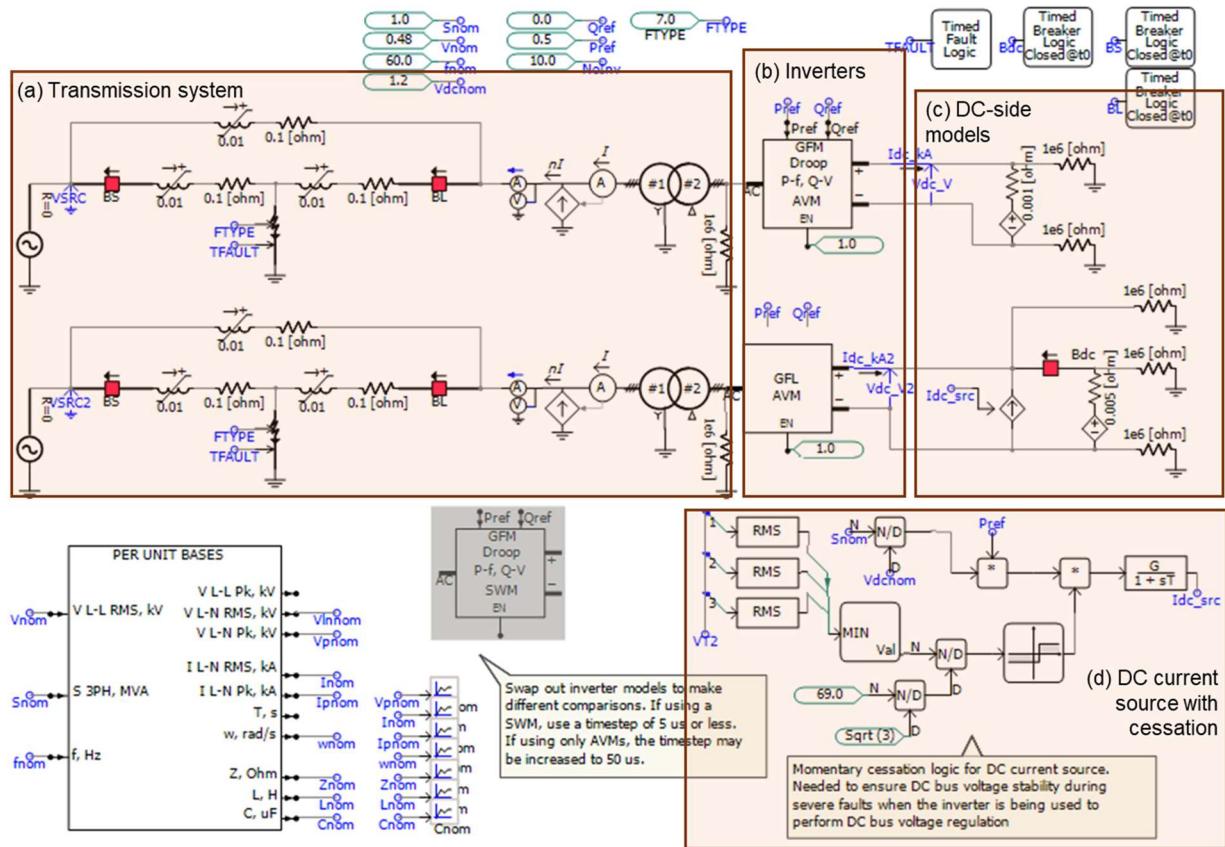

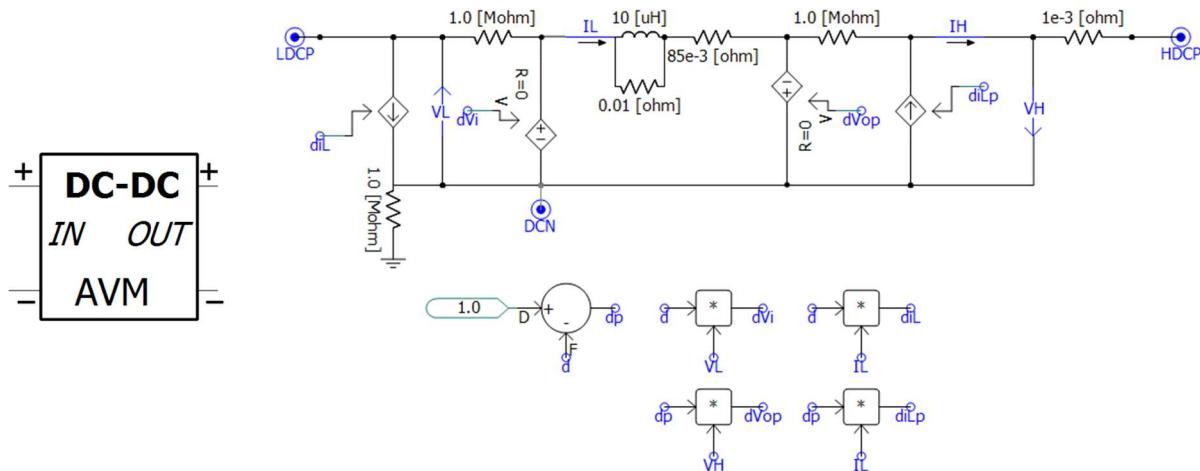

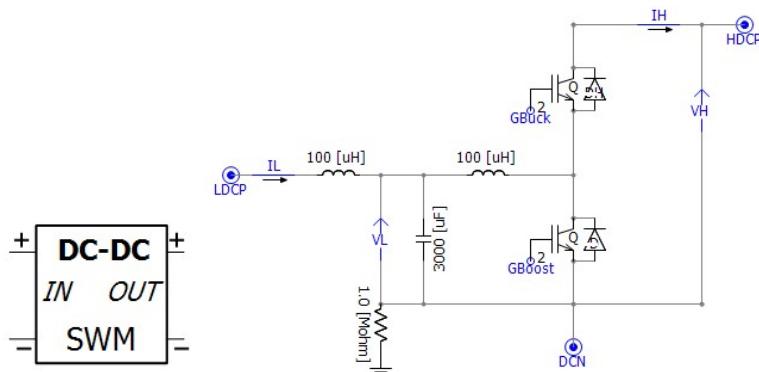

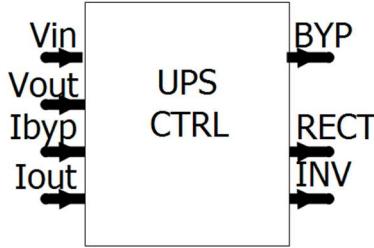

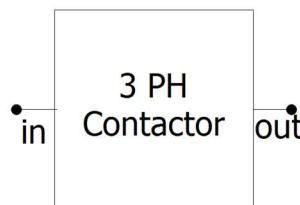

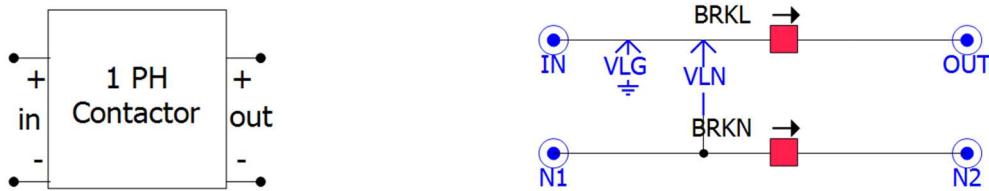

Table 2: Kinds of Oscillatory Interactions Data Centers Could Contribute to.